Technology resurges as industry pushes to 7nm and 5nm.

Nearly 10 years ago, the industry rolled out a potentially disruptive technique called inverse lithography technology (ILT). But ILT was ahead of its time, causing the industry to push out the technology and relegate it to niche-oriented applications.

Today, though, ILT is getting new attention as the semiconductor industry pushes toward 7nm, and perhaps beyond. ILT is not a next-generation lithography (NGL) tool technology. Instead it falls into the field of computational lithography and is used for the production of advanced photomasks.

ILT is a next-generation reticle enhancement technique (RET) that enables an optimal photomask pattern for both optical and extreme ultraviolet (EUV) lithography reticles. Using a complex mathematical formula, ILT improves the latitude of a process and the depth of focus for a lithography tool.

Ultimately, the industry hopes to devise “full-chip ILT masks,” which involves the integration of the technology for all layers, not just for some isolated features on the reticle. Full-chip ILT may help ease the constraints in advanced patterning, as the technology could enable the most difficult features, such as tiny contacts, cuts and vias, in IC designs.

Today, ILT is used in niche applications, mainly for hot spot repair on the mask. But now, the industry is finally moving closer toward full-chip ILT masks for advanced IC designs at 7nm and/or 5nm.

In fact, the ecosystem is falling into place for full-chip ILT. The EDA tools are ready. But the biggest breakthrough occurred when a tool vendor recently rolled out the world’s first multi-beam mask writer, which promises to reduce the write times for full-chip ILT masks from weeks to hours.

“The industry has totally changed its attitude,” said Linyong “Leo” Pang, an ILT pioneer who is chief product officer and executive vice president at D2S. “In the beginning, when we introduced ILT, the mask industry was skeptical. Then, two years ago, they said: ‘ILT is coming.’ This time, everyone is saying they are ready.”

To be sure, full-chip ILT is a key enabler. “ILT is another RET,” said Vivek Singh, a fellow and director of computational lithography at Intel. “So, it’s a technique to sharpen the image somewhat for specific conditions of layout pitches. It obviously works better when you are pushing the density. It also works better when you are trying to make small features like vias.”

But there are still some challenges to implement full-chip ILT. “(The challenge is) to translate those masks into manufacturable ones,” Singh said.

Why ILT?

Initially, ILT was the subject of research at universities in the 1980s. Then, in 2007, a now-defunct company called Luminescent Technologies rolled out what was considered the world’s first commercial ILT products.

Instead of using traditional rectangular features on the mask, ILT makes use of tiny and complex curvilinear patterns that resemble Rorschach ink blot tests. ILT works in conjunction with various lithographic technologies, such as 193nm immersion, directed self-assembly (DSA) and EUV.

“The idea of ILT is simple,” said D2S’ Pang, who was a former executive of Luminescent from 2004 to 2014. “You know something that you want to print. If you can model the scanner optics, then you can inversely calculate what’s on the mask. So, that would give you the pattern fidelity and the best process window.”

In the mid- to late-2000s, there was a pressing need for ILT. At the time, lithography tools were patterning chips beyond the wavelength of light. Diffraction and other issues were becoming an obstacle for lithography and the photomask.

The photomask is a critical part of the IC supply chain. A chipmaker designs an IC, which is then translated into a file format. Then, a photomask is developed based on that format.

Basically, the photomask is a master template for a given IC design. After a mask is developed, it is shipped to the fab. The mask is placed in a lithography scanner. The scanner projects light through the mask, which patterns the images on a wafer.

Diffraction occurs when a beam of light passes through the scanner to the mask. The light waves spread out, and sometimes are accompanied by interference. Therefore, a pattern could become blurred or lost.

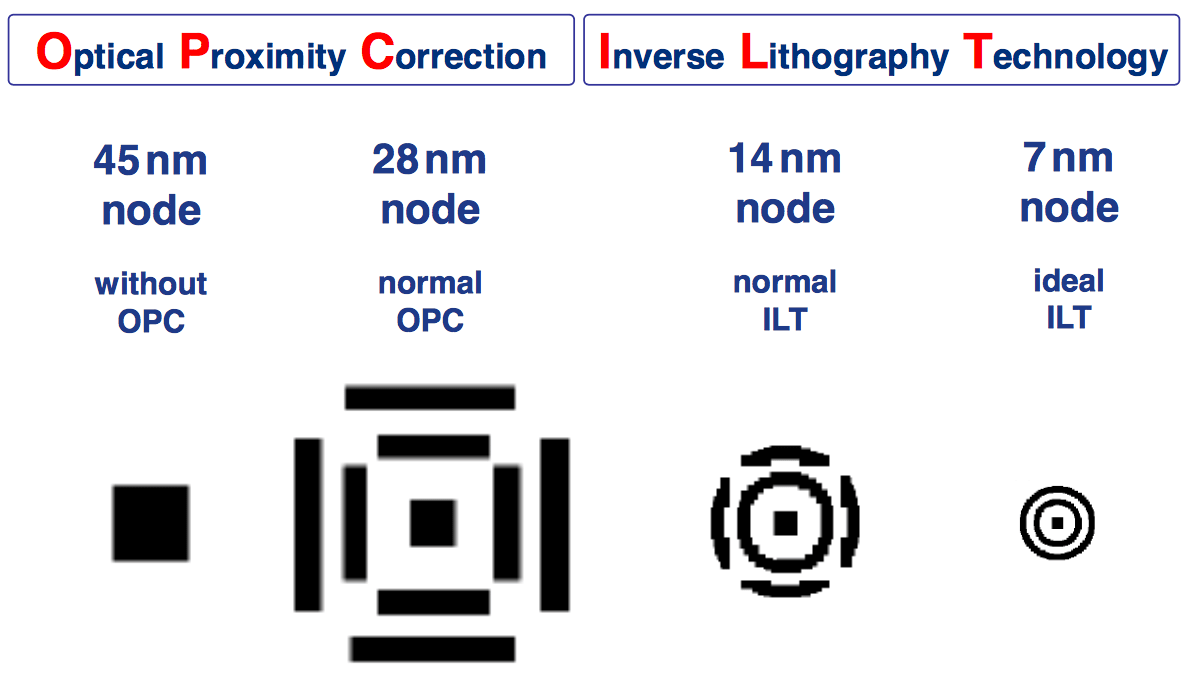

To deal with the diffraction issues, mask makers use various RETs on the photomask. One RET, called optical proximity correction (OPC), is used to modify the mask patterns to improve the printability on the wafer. OPC makes use of tiny sub-resolution assist features (SRAFs), or decoration-like shapes, on the mask.

At that time, OPC features were (and still are) becoming smaller and more complex at each node. And as a result, the e-beam mask writer tool took a longer time to pattern a mask, thereby impacting photomask turnaround times and costs.

Meanwhile, to address those issues, Luminescent proposed ILT for the 45nm and 32nm nodes in 2007. ILT goes beyond OPC. OPC perturbs the mask patterns, enabling mask makers to print what they want to print.

In contrast, for ILT you have patterns that you want to print on the wafer. Then, you formulate target patterns and model the scanner optics and resists. Finally, you inversely calculate the desired mask pattern.

At the time of its launch, however, ILT wasn’t ready. For one thing, the write times for an ILT mask were too long and expensive. “Basically, the idea was to improve the resolution,” Pang recalled. “At 45nm, though, immersion was introduced. That actually delayed the need for ILT.”

As a result, ILT was pushed out, at least for mainstream applications. All told, OPC became the standard RET technology for masks at 100nm and below. Today, chipmakers use OPC for leading-edge masks.

Following those events, Synopsys acquired the computational lithography technology from Luminescent in 2012. Since then, Synopsys has been selling an ILT product that came from this acquisition. The product is called Proteus ILT.

Then, in 2014, KLA-Tencor acquired the inspection/metrology technology from Luminescent, which no longer exists.

Generally, ILT has been used for hot spot repair on the mask. But until recently, the industry has generally avoided full-chip ILT—it has been simply impractical. “You can build a mask today with ILT using the existing VSB (variable shape beam) e-beam writers, but it would take a prohibitively long time,” said Mark Wylie, product marketing director at KLA-Tencor. “Write times for a typical mask could be 8, 12 or 24 hours. With ILT, I’ve heard it could be significantly longer, like up to 5 days. It gets very unwieldly. That’s why it’s not in the mainstream.”

Is ILT ready?

ILT is heating up again, though, and for good reason. Leading-edge masks are becoming too complex and expensive. Multi-patterning is driving up mask complexity. And there is a pressing need to print smaller features and more complex shapes on the mask.

There are other factors. At 28nm and above, for example, the features and shapes on optical masks are more simple and rectangular. Starting at 20nm, the shapes began to move toward more complex and curvilinear features.

As a result of mask complexity, the write times for a photomask have increased by about 25% a year since 2011. This, in turn, impacts mask turnaround times and cost.

Fortunately, there is hope for the industry. Recently, IMS Nanofabrication introduced the world’s first commercial multi-beam mask writer. Equipped with 262,144 beams, the system can write a complex optical mask in just 10 hours, compared to 30 hours for a traditional VSB tool.

NuFlare is also working on a multi-beam mask writer tool. This technology is important for several reasons. First, it can reduce the write times for both optical and EUV masks. Second, it could also cut the write times for full-chip ILT masks, thereby making ILT a reality.

“The multi-beam writer, as we built it, will enable much more complexity on ILT, aggressive OPC and maybe pixilated masks,” said Elmar Platzgummer, chief executive of IMS. “All of those things have been investigated. But often, it was not adopted because the write times were not supporting any reasonable manufacturing of such masks.”

Fig. 1: Increasing mask pattern complexity. Source: IMS Nanofabrication.

Today’s e-beam tools that write masks use variable-shaped rectangular shots at precisely defined locations. By using large and small rectangles all with Manhattan orientations, any reasonably shaped circuit element can be drawn. With a VSB tool, mask makers can pattern curvilinear and ILT-like shapes. This requires a multitude of shots, however. Each one takes a long time.

To solve the problem, the industry came up with a solution—overlapping shots. With this, VSB tools can write complex curvilinear patterns with fewer shots. Ultimately, though, you need multi-beam mask writers. Multi-beam is an array of beams. It can basically write in pixels and can take angular shots, making it ideal for ILT. It doesn’t matter what types of shapes you write. And the write times are constant.

Besides multi-beam mask writers, the industry needs the EDA tools to enable ILT. Today, Mentor Graphics and Synopsys sell ILT-based tools.

Once the ILT masks are developed, they must be inspected. For this, KLA-Tencor recently rolled out two 193nm optical mask inspection systems for use at 10nm and 7nm. “That was one of the driving factors for developing these inspection systems,” KLA-Tencor’s Wylie said. “This allows us to inspect and enable ILT.”

While the ecosystem is falling into place, there are still some big questions. Will the industry ever develop full-chip ILT masks? If so, when? And what are the benefits and challenges?

Generally, the industry hopes to enable full-chip ILT masks at 7nm. But this all depends on whether mask makers will insert IMS’ multi-beam mask writer tools for production at 7nm. If not, full-chip ILT could slip to 5nm.

Regardless, the benefits of full-chip ILT are clear. “The process window on the scanner is becoming very narrow. Depending on the devices, it could be 50nm to 60nm depth of focus,” KLA-Tencor’s Wylie said. “What ILT brings to the party is that it will give you more process latitude by about 5% to 10%, depending on the type of layer and geometry you are trying to nail.”

On the device side, full-chip ILT is ideal for contacts, cuts and vias in advanced designs. “Not every layer requires ILT. If you do a line/space layer, you don’t need ILT. But for contact and via layers, it could be done with OPC or ILT,” D2S’ Pang said. “(With ILT), you can go to smaller pitches. So the chips would be denser. This would give you more room in the design rules.”

So chipmakers want tiny contacts, but with scaling the contact becomes even smaller. “You start to see diffraction patterns,” Pang said. “Then, on the wafer plane, this dot is getting fuzzy. Then, you also see interference rings along it.”

Basically, ILT creates extra patterns on the mask plane. “It will basically mitigate the rings as much as possible or make them disappear,” he said.

For this reason, ILT is also ideal for multiple patterning. But will ILT solve all of the problems for mask makers and lithographers? “This is not so much a paradigm shift, but a continuation of many years of computational lithography research and development,” said David Fried, chief technology officer at Coventor. “Rules-based OPC started this trend long ago. Then, we progressed to model-based OPC and source-mask optimization. Each of these steps improves the pattern fidelity we’re able to achieve with a given lithography tool. ILT should extend the capabilities of 193i for 2D pattern complexity issues. It will not, however, improve the fundamental 1D minimum pitch capabilities of 193i.”

On top of that, there are still some major challenges for ILT, even with multi-beam mask writers. “Mask complexity and runtime are the two biggest hurdles for ILT adoption,” said George Bailey, director of technical marketing within the Silicon Engineering Group at Synopsys. “So this is why our customers are adopting solutions that are incrementally complex with each node. Our customers have several ways to minimize mask complexity and runtime while maximizing their process windows. For example, they can choose a localized application like cell-level optimization or hotspot fixing, but they can also control their mask complexity by choosing from a highly-effective free-form mask to a more traditional Manhattanized mask. Obviously, with the introduction of multi-beam mask writers, mask complexity becomes less of an issue, which is an option that some Proteus ILT customers are considering.”

Fig. 2: ILT increased common depth of focus by 43nm. Source: Synopsys.

There are other issues as well. “Full-chip ILT is already in reach for highly hierarchical designs like multi-core logic chips or memory chips,” said Ingo Bork, a product manager from Mentor Graphics.

“Multi-beam mask writers are intended to decouple data complexity from write times,” Bork said. “From an EDA vendors perspective, I see a possible limitation in the use of MPC. Selective dose assignment of small features is a very powerful way of pushing resolution limit and CD uniformity on masks written on VSB writers and is used in what we call dose-based MPC. With dose-based MPC applied and all corrections included, a small isolated feature can easily require 4x the dose of a large nested feature.”

On VSB writers, this is not a problem since using a high dynamic range of dose levels does not have a large effect on mask write times. “This is not the case for multi-beam writers, where the highest dose level used is directly proportional to the write time of the entire mask even if this high dose level is required for selected features only,” Bork said. “On the other hand, multi-beam writers are reputed to have high enough beam-current density to make use of low sensitivity, high resolution, non-chemically amplified resists. This may reduce the impact of stochastic effects inherent to chemically-amplified resists, which would in turn reduce the need for selective dose assignment.”

EUV and ILT?

At 7nm, meanwhile, the industry is moving in two directions. Some chipmakers will extend 193nm immersion and multiple patterning to 7nm, while others hope to insert EUV. Based on 13.5nm wavelength technology, EUV promises to simplify the patterning flow, thereby reducing the mask count.

But EUV is still not in production. There are persistent issues with the power source, resists and mask infrastructure.

So, some won’t insert EUV at 7nm. “Our first 7nm will be based on optical lithography, and we have a migration path to EUV,” said Gary Patton, chief technology officer at GlobalFoundries, at a recent event. “We are betting on EUV, but we are not (planning to insert it) on 7nm. That would be a critical mistake based on the schedule our customers are on.”

Others do hope to insert EUV at 7nm. With optical lithography and multi-patterning, the mask count is expected to reach about 80 to 85 layers at 7nm, compared to 60 at 16nm/14nm. “We think maybe one or two companies can afford this technology (at 7nm),” said Kelvin Low, senior director of foundry marketing at Samsung.

But if EUV does happen at 7nm, the technology will still require a multiple patterning scheme. “We think EUV and multi-patterning are complementary,” said Harmeet Singh, vice president of dielectric etch products at Lam Research. “Whenever EUV is introduced, multi-patterning will help enable it.”

EUV masks, meanwhile, will require complex SRAFs and perhaps ILT. “ILT technology actually supplements EUV since the initial hardware is being shipped with a low numerical aperture (NA),” Synopsys’ Bailey said. “The resolution loss due to low-NA imaging can be offset with ILT, and we are aware of research being performed on this exact application. Another thing to consider is that EUV will only be utilized on layers with the best cost savings, such as the quadruple-pattern layer down to the double-pattern layer. But the other layers would utilize ArF scanners, where ILT could reduce a double-pattern layer down to a single-pattern layer. This layer reduction is a common ILT use model today.”

To be sure, full-chip ILT masks are complex. It’s perhaps too expensive for most. Still, full-chip ILT stands a fighting chance, at least this time around.

Related Stories

Deploying Multi-Beam Mask Writers

Multi-Beam Market Heats Up

Executive Insight: Aki Fujimura

Reference the paper, if possible to combine OPC or ILT with the mask optimization in z direction, i.e. absorber thickness, to enlarge process window?

ILT has really helped single exposure at lower k1. It could reduce exposures for self-aligned quadruple patterning.