Technology shifts direction after years of competing directly with CMOS at advanced nodes.

Fully depleted silicon-on-insulator (FD-SOI) is gaining ground across a number of new markets, ranging from IoT to automotive to machine learning, and diverging sharply from its original position as a less costly alternative to finFET-based designs.

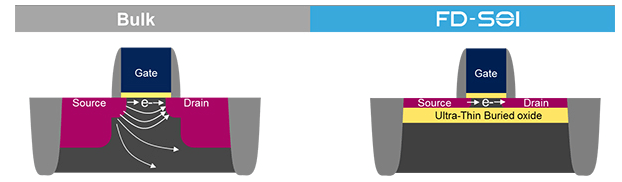

For years, FD-SOI has been viewed as an either/or solution targeted at the same markets as bulk CMOS. Among the differences:

FD-SOI also does not require channel doping, which is where the term “fully depleted” comes from. It is scalable at least to 10nm, according to Leti. And it can be sourced at both GlobalFoundries and Samsung, with more capacity under development in China at GlobalFoundries’ new fab in Chengdu and possibly more on the way from Shanghai Huali Microelectronics Corp. (HLMC).

All of those factors have contributed to FD-SOI’s growth. But the momentum appears to be building almost independently of the aggressive advanced-node roadmaps for the mobile and server world, where EUV, taller finFETs, gate-all-around FETs, and increasingly smaller features remain the central focus.

Fig. 1: Bulk CMOS vs. FD-SOI. Source: STMicroelectronics

In the past, even new applications might have taken the usual scaling route. But two things have changed recently. First, there are fewer companies and applications that can afford the most advanced-node device scaling, particularly after 10/7nm. The smartphone market is flattening, and the volume of chips being shipped based on any single design are shrinking as a number of smaller players such as Xiaomi and Oppo begin eating into market share held by Samsung and Apple. And second, there are new markets emerging where power is a critical element in design, and where costly designs no longer equate to billions of units. This is why Apple has begun using TSMC’s Integrated Fan-Out (InFO) approach to add flexibility into its designs.

Those market shifts help to make FD-SOI a more viable option, and there are enough new markets where no technology is the clear winner at this point. This has resulted in significant growth for FD-SOI, particularly in the past year, in markets such as the inferencing stage of machine learning, base-stations, IoT and IIoT, bitcoin mining, 5G, radar, and a variety of automotive applications.

“This has been a good strategy for FD-SOI,” said David Fried, vice president of computational products at Coventor, a Lam Research company. “It’s got a different position in cost, performance and manufacturing readiness. So competing for the same markets/products as the huge 14nm finFET logic foundry providers would have been a complex comparison, and probably a losing proposition. FD-SOI fundamentally enables some different circuit topologies, such as back-biasing and dynamic control, which have made it appetizing for some of these adjacent markets.”

IoT/IIoT and automotive are at the top of the list of new market opportunities for FD-SOI.

“For NB-IoT (NarrowBand IoT), 22FDX makes deployment affordable because you can integrate four to five chips into one and still run logic at 0.4 volts and memories at 0.5 picoamps per cell,” said Jamie Schaeffer, 22FDX program director at GlobalFoundries. “With automotive, there’s great potential for body electronics because of the ability to integrate ultra low power and RF and devices for 5-volt analog interfaces. You also can add embedded MRAM, which provides low-cost security in the automotive space. Another place we’re seeing it is in 77 GHz radar, where you integrate the front-end module with the transceiver. And we’re seeing it in device stacking because there is not the same kind of substrate loss that you get with other materials.”

Pros and cons

FD-SOI has a couple of well-understood advantages. One is that it is a planar technology, which makes it simpler to design, manufacture and test. The first layer consists of an ultra-thin buried oxide, which is added onto a silicon substrate. Because it is so thin, there is no reason to dope the channel.

Second, the insulator layer reduces the capacitance between the drain and the source, which in turn allows chipmakers to deploy body biasing, which is a way of optimizing a circuit’s power and performance by tuning the threshold voltage. In effect, the circuit is either powered on more quickly or slowly as needed by utilizing the difference between the source voltage and the body voltage.

So far, most of the body biasing has been uni-directional. That will change at future nodes, and there are workarounds even today.

“At 28nm and 22nm, back biasing is not bi-directional,” said Giorgio Cesana, director of technology marketing at STMicroelectronics and executive co-director of the SOI Industry Consortium. “You can go forward or reverse, although this hasn’t been a problem because you can center on a point that is not zero. So, effectively, you can get bi-directional biasing. But with the next-generation nodes, GlobalFoundries is planning to add bi-directional biasing.”

That adds an even wider swing to this power-saving technology. The disadvantage is that reverse biasing can add stress to a system, which accelerates circuit aging. Proponents dispute that, saying adaptive body biasing can compensate for that stress.

Fig. 2: Adaptive body biasing to counter aging effects. Source: Soitec/Philippe Flatresse

“With adaptive voltage scaling techniques, you actually can play with the voltage using back and body biasing to compensate for aging,” said Christophe Maleville, vice president of the digital business unit at Soitec. “So not only is there no reliability issue, but you can correct for aging. You are actually improving the design margin for aging.”

This requires a fair degree of expertise, however. As with all things related to power, nothing is easy.

“SOI obviously has its complexity,” said Coventor’s Fried. “But there have been several SOI technologies put into volume manufacturing in 300mm (albeit PD-SOI, where the device layer is significantly thicker). The wafer manufacturing community has learned a lot of the lessons over the years about defectivity and uniformity. There are many differences in the overall process, so comparisons can get complex. But here are a few-in FD-SOI, the STI module can be much simpler. Isolation is easy, so there is no deep trench to etch. On the other hand, the thickness of the extremely thin device film has a direct impact on the threshold voltage of the transistor. This is a variation that’s new and specific to this technology. PD-SOI doesn’t even have this direct sensitivity. And finally, for some of these advanced circuit topologies, the buried dielectric layer has some implications on the coupling to the devices, and any active control of back-biasing would be a bit new for this technology.”

At this point, the biggest nodes for FD-SOI are 28nm and 22nm. Cesana said 12nm is under development at GlobalFoundries, and Samsung is working on 18nm. The roadmap can be extended further if there is a business reason to make that happen. “But the kind of products affected by FD-SOI are not the ones where you need to offer a new node every year. If you look at RF and millimeter-wave technologies, they don’t move because they can shrink features. They move for extra power savings, which is why we think companies will stay on 28nm and 22nm for a very long time.”

New markets

That fits well with automotive and industrial IoT applications, where most chips need to be robust but not necessarily at the leading-edge processes.

“FD-SOI exhibits 100X to 1,000X lower radiation effects than other types of chips,” said Soitec’s Maleville. “That’s a big issue for automotive companies. So is low power. Car companies want to use chips in different areas without having to add cooling units. If you can have a lower operating temperature, you also improve the reliability of the devices.”

That has pushed some big-name companies into the FD-SOI world, including NXP and Intel. NXP is offering multiple platforms for different markets based upon FD-SOI. Intel, meanwhile, rejected FD-SOI in favor of bulk CMOS for its processors. But it essentially bought its way into the market last year when it purchased Mobileye, which uses FD-SOI for its self-driving technology, at least for the current generation of EyeQ4 autonomous driving chips. The company plans to move the technology to 7nm finFETs in 2020 with the EyeQ5, which will support level 4 and 5 autonomous driving, but power consumption will increase from 3 watts to 10 watts based upon that change.

The technology also is gaining ground in the bitcoin mining world, as well, which is notoriously energy-intensive.

“You want as much computing power as you can possibly get for bitcoin, but you also want the least amount of compute power needed to get the job done,” said Maleville. “So you really want to compute at 0.35 or 0.4 volts and use as many cores as possible. FD-SOI supports 0.35 volts for processing and 0.35 volts for memory.”

Material shifts

None of this happens quickly, of course. CMOS has been in continuous use since it was first patented by Fairchild Semiconductor in 1963, and an entire supply chain and manufacturing flows have built up around it.

“One of the big barriers has been the lack of an ecosystem,” said GlobalFoundries’ Schaeffer. “Part of this was inertia. It’s taken awhile for customers to recognize the value of FD-SOI. There was a long gestation period for RF millimeter-wave and LP millimeter-wave. And customers are just starting to unlock the full potential of body bias. There were investments companies needed to make. Part of that is being driven by machine learning. In the training phase, which is typically done in a data center, you want the highest performance possible, which is often 2.5D with multiple HBMs. But for inference, you want to do some of that in the edge devices where you balance compute, power and cost. That can involve RISC-V, DSPs, embedded memories and FD-SOI, because you want ultra low voltage and low junction capacitance.”

Most of this happens at a level that the semiconductor supply chain rarely sees. But as new markets open up, chipmakers are finding themselves much closer to the application than in the past.

“It generally doesn’t matter whether it’s bulk CMOS or FD-SOI for soft IP,” said Rupert Baines, CEO of UltraSoC. “The impact of FD-SOI is at the architectural level for power control, and anyone doing RISC-V has an architectural license. But the one area where it does crop up is in automotive, where our IP is being used for resilience.”

Conclusion

So what does all this mean for the semiconductor industry? At this point, it’s too early to tell. Making predictions about materials and processes has defied prognostications for years. But FD-SOI is well proven in the market, as is RF-SOI. And while it will likely not be used for the most advanced nodes, even there bulk CMOS has been the topic of discussions for the past few years, along with other materials that can replace it. At last count, there were more than 20 possibilities for transistors at 3nm and beyond based on a number of different materials. There are options for FD-SOI, as well.

Fig. 3: Evolutionary path for FD-SOI. Source: Soitec

If history is a guide, changes will be evolutionary whenever possible, and they will always happen more slowly than most people anticipate. But in new markets anything is possible, and FD-SOI is much closer to evolutionary than revolutionary. And with a growing ecosystem, that could make it an interesting choice for a wide range of applications.

Related Stories

Inside FD-SOI And Scaling

GlobalFoundries’ CTO opens up on FD-SOI, 7nm finFETs, and what’s next in scaling.

Bulk CMOS Vs. FD-SOI

28nm and 22nm are becoming much more interesting process nodes.

Predictions: Manufacturing, Devices And Companies

New architectures, materials and equipment could have a huge impact on the chip industry.

Tech Talk: FD-SOI Vs. FinFET

Cost, performance, multi-patterning and the 12nm roadmap.

SOI has been tomorrows technology since the 90s.. it is great for reasons you mentioned but the wafer cost ends up being higher (unless you ask a PRO SOI company.

is tsmc using soi?

what is 300mm bare wafer cost?

In 2016, about 450 USD.