DARPA and a number of major vendors are backing this modular approach, but hurdles remain.

Momentum is building for the development of advanced packages and systems using so-called chiplets, but the technology faces some challenges in the market.

A group led by DARPA, as well as Marvell, zGlue and others are pursuing chiplet technology, which is a different way of integrating multiple dies in a package or system. In fact, the Defense Advanced Research Projects Agency (DARPA), part of the U.S. Department of Defense, hopes to drive standards and a new ecosystem for its chiplet program, dubbed Common Heterogeneous Integration and IP Reuse Strategies (CHIPS). Boeing, Cadence, Lockheed, Intel, Northrop Grumman, Micron, Synopsys and others are involved in the CHIPS program, which is targeted for commercial and military/aerospace applications.

There are several approaches to chiplets. The basic idea is that you have a menu of modular chips, or chiplets, in a library. Then, you assemble chiplets in a package and connect them using a die-to-die interconnect scheme. In theory, the chiplet approach is a fast and less expensive way to assemble various types of third-party chips, such as I/Os, memory and processor cores, in a package.

“(With chiplets), you can actually start composing systems like LEGOs,” said Andreas Olofsson, program manager in the Microsystems Technology Office at DARPA. “If we can truly have an ecosystem of hundreds or thousands of tiny chiplets sitting on the shelf, then we can talk about having days to weeks of doing state-of-the-art design.”

So far, the industry has developed some packages using the chiplet-like approach, at least in limited volumes. But the goal is to make chiplets a more mainstream option. For this, though, the industry may require standards, a broad array of chiplets, design tools and new manufacturing techniques.

Regardless, the market for multi-die packages like chiplets and others are heating up, and for good reason—they are possible alternatives to traditional chip scaling. In scaling, you shrink the features of a device at each node, enabling a smaller die with more functions. But IC scaling is becoming more expensive and the benefits are shrinking at each node.

Another way to get the benefits of scaling is by integrating multiple and different dies in an advanced package, sometimes called heterogenous integration. 2.5D/3D, fan-out and system-in-packages (SiPs) are examples of heterogeneous integration in packaging. The chiplets approach is another option.

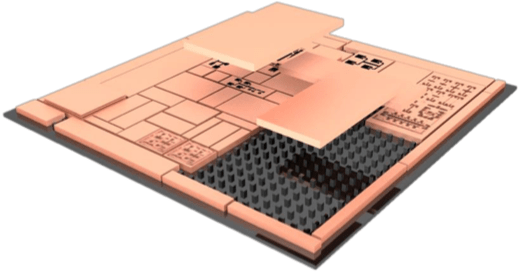

Fig. 1: Monolithic die using chip scaling vs. modular chiplet approach Source: DARPA, Intel

No one package type can meet all requirements, so customers will likely use many technologies. “There are many options for heterogenous integration and each will have its place,” said Jan Vardaman, president of TechSearch International. “No one size fits all.”

In the case of chiplets, though, the technology faces several challenges to become a mainstream option. “It looks easy in PowerPoint,” Vardaman said, “but real product is likely to be a bit more challenging. Good design and high yield are essential to success.”

And not all chiplet approaches are alike, as each group has a different twist. Plus, the chiplet market is confusing and it’s unclear if it will ever live up to its promises.

To help the industry get ahead of the curve, Semiconductor Engineering has taken a look at the various chiplet approaches.

Chiplet challenges

The chiplet concept isn’t new. The technology can be traced to the 1980s, when the industry developed multi-chip modules (MCMs). In MCMs, you integrate dies and connect them in a module.

At that time, MCMs were relegated to high-end systems like mainframes. For other systems, the industry used commodity packages. All told, packaging was an afterthought in the IC market.

That started to change in more recent times, when the industry realized that chip scaling was becoming more expensive and complex at each node. Today only a select few can afford to design chips at advanced nodes. For example, IC design costs alone have jumped from $51.3 million for a 28nm planar device to $297.8 million for a 7nm chip, according to International Business Strategies (IBS).

Beginning just after the turn of the millennium, the industry began to look for alternatives, namely advanced packaging. Instead of scaling the features on a monolithic die, the idea behind advanced packaging is to go in the vertical direction.

This is not to say that chipmakers have stopped scaling. On the contrary, chipmakers are ramping up 10nm/7nm with 5nm in R&D. In addition, advanced packaging hast been use in limited form for decades for niche applications

For many customers, though, advanced packaging has emerged as a parallel or alternative path to scaling at the leading edge of design, with several options on the table. For example, the industry has been shipping 2.5D technology. In 2.5D, dies are stacked on top of an interposer, which incorporates through-silicon vias (TSVs). The interposer acts as the bridge between the chips and a board, which provides more I/Os and bandwidth.

Then, several years ago, fan-out emerged. In fan-out, the dies are packaged while they are still on the wafer.

And not long ago, the chiplet approach emerged, which is a different way of building devices. With an SoC, a chip might incorporate a CPU, plus an additional 100 IP blocks on the same chip. That design is then scaled by moving to the next node, which is an expensive process.

With a chiplet model, those 100 IP blocks are hardened into smaller dies or chiplets. In theory, you would have a large catalog of chiplets from various IC vendors. Then, you can mix-and-match them to build a system. Chiplets could be made at different process nodes and re-used in different designs.

That’s what the CHIPS program and other efforts are trying to accomplish. “For instance, a lot of IP cores that you buy are quite expensive or not available in a process technology from every vendor. It might be available in another process,” said Craig Hornbuckle, CTO at Jariet, an analog/RF design house and member of DARPA’S CHIPS program. “In CHIPS, you can put together an integrated device and form what you need. That’s an advantage.”

This approach solves other issues. “The advanced process nodes are geared toward digital. They are not geared for high-performance analog. As designers, we adapt to those applications, but it’s challenging and takes a long time. (With chipets), you can use a particular node for an application,” Hornbuckle said.

There are other benefits, too. “One of the main purposes of chiplets is to find an option to reduce the design cycle time/cost consideration facing SoC design, assuming relatively equivalent performance,” said Choon Lee, vice president of advanced packaging at Lam Research. “The chiplet concept can be applied to the performance-first applications, for example, military or aerospace.”

Still, there are some challenges to making this work. Among them:

• Currently, there is no standard way of assembling or packaging chiplets.

• The die-to-die interconnect schemes can be expensive.

• There are design and manufacturing gaps, such as how to verify and test chiplets.

• It is unclear who takes responsibility for the chiplets once they are manufactured and handed off to the integrator or packaging house.

Clearly, design and test considerations are key. “Chiplet design should be included in a system design around the main active chips. It requires interconnection/functional test compatibility between the external world to chiplets and from chiplets to main chips, which involves the whole module yield issue,” Lee said.

Others agree. “While chiplets sound great in theory, there are still several challenges to overcome before a combined chiplets approach is really ready to topple the juggernaut SoC model,” said John Ferguson, marketing director for DRC applications at Mentor, a Siemens Business. “While the individual cost to manufacture each chiplet may come down compared to their corresponding embedded IPs in a single process, there are still other costs and risks. With the development and support of dedicated PDKs, foundries made the design of SoCs relatively easy and low-risk. As we move toward an approach that involves individual chiplet design teams (in-house or third-party), the design-to-manufacture flow for combining these chiplets into a single package is still in its infancy.”

Part of the problem is that a chiplet approach implies multiple manufacturing and supply chains. That makes it difficult to capture a single recipe to ensure all the chiplets work individually, and in the context of a package with other chips.

“While a chiplet can theoretically be re-used in multiple designs, each chiplet will have its own set of limitations on how and where it can be used, depending upon the specific implementation,” Ferguson said. “How dies interact will determine a great deal about how they can be used in a given context. Will they connect by solder bumps or direct bonding? Are TSVs required for back-side access? What sort of test protocols have been built into each chiplet?”

As with any chip or package, yield is key. “Integrating chiplets into a system-in-package will drive increasingly high-density interconnections. Whether the chiplets are assembled using a silicon interposer, a silicon bridge, or high-density fan-out, the trend on the chiplets will be smaller and finer-pitch micro-bumps,” said Stephen Hiebert, senior director of marketing at KLA-Tencor. “These micro-bump interconnects have to be defect free, which drives 100% screening inspections with no escape of killer defects. In addition, the silicon interposer, silicon bridge, or silicon-less redistribution layers used to connect the chiplets must be of both high quality and high yield because of the cumulative value of IC content being assembled.”

Another issue is that who will take charge of a given project. “Chiplets may see first adoption from a turnkey IDM or a foundry who can control manufacturing of the chiplets and packaging and assembly of the chiplets into a system,” said Nirmalya Maity, vice president of packaging at Applied Materials. “This avoids the potential problem of sourcing commodity chiplets from different vendors and having quality and compatibility variations, which may affect system performance. Having a turnkey supplier also reduces many of the adoption delays associated with multi-vendor, complex supply chains. For example, when multiple suppliers and services are involved, who takes responsibility for system yield and performance? And how does one test components and sub-systems to ensure they are good prior to committing them to the assembly?”

Cost, of course, is the most critical factor. “CapEx and cost of ownership sensitivity is another big constraint,” Maity said. “These factors drive the need for cost-effective, innovative solutions.”

The commercial vendors

Marvell and Kandou Bus were the first to jump on the chiplet concept. They announced a deal in 2016 under which Marvell would use Kandou’s chip-to-chip interconnect technology to tie multiple chips together.

Fig. 3: Fully modular MCM-based SoC. Source: USR Alliance

Kandou is developing an ecosystem of small and midsize companies, and has agreed to give up some of its IP to others to jump-start this approach. Marvell is building a switch based on Kandou’s interconnect technology.

“If you want to integrate everything onto a single die, it takes longer. If you want to go to advanced processes, it costs more,” said Amin Shokrollahi, CEO of Kandou Bus.

Reducing the cost of developing new chips is critical for a number of markets. “What we’re looking at with chiplets is a massive disintegration,” Shokrollahi said. “There is an army of small companies doing one thing and one thing only, and this allows them to get to market quickly. So, if you think about a small company developing a network interface card, they can combine their technology with a few other things and get a working prototype out the door very quickly. The big shift is that with chiplets, small companies can afford to innovate.”

Last year, startup zGlue announced a technology that stacks chiplets in a package. zGlue isn’t making its own chips. Instead, it is amassing a portfolio of off-the-shelf chips from third parties.

These third-party chips are already produced in the fab and packaged using chip-scale packages (CSPs). The company also plans to support known good die (KGD) and LGAs.

What zGlue provides is a proprietary platform or module, as well as an active interposer. The base of the module consists of a PCB and circuitry. The module itself is configured in a BGA package.

Inside the platform or module, the chiplets are placed on the company’s mesh-like fabric, which serves as an active programmable interposer. The 130nm interposer is made on a foundry basis by TSMC. ASE handles the assembly process for zGlue.

“We have a mechanism that we can take wafer-level chip-scale packages from different vendors without putting on any restrictions and we use them as is,” said Jawad Nasrullah, CTO of zGlue. “(The active interposer) is kind of like a surface of distributed micro pillars, just like Velcro. And you put chips down on it using surface-mount technology. Based on the intention and what is actually produced, you can do some corrections for it. All of the connectivity is done by software. There are really no hardwires that are being drawn with the exception of just a few in some areas.”

Fig. 4: A system block diagram using zGlue’s technology Source: zGlue

Today, zGlue is focusing on select applications in the connected space, such as Bluetooth, narrowband IoT, WiFi and wearables. A year ago, zGlue had a portfolio of 10 chiplets from third parties. Now, it has more than 100 chiplets from 30 to 40 companies, with plans to have 500 over time. ADI, Dialog, Macronix and Vishay are just a few of the chiplet vendors in the company’s portfolio.

DARPA’s approach

In 2016, DARPA released a solicitation for bids from outside companies for its CHIPS program. The goal was (and still is) to devise a modular design and manufacturing flow for chiplets. DARPA also plans to develop a large catalog of third-party chiplets for commercial and military apps. All told, the CHIPS flow is expected to lead to a 70% reduction in design cost and turn-around times.

The CHIPS program started in 2017. The program has various types of contractors/sub-contractors—manufacturers (Intel, Northrop, Micross and UCLA); chiplet developers (Ferric, Jariet, Micron, Synopsys, and University of Michigan); and EDA suppliers (Cadence and Georgia Institute of Technology).

CHIPS is one of several programs within DARPA’s Electronics Resurgence Initiative (ERI). ERI is a five-year, upwards of $1.5 billion investment to fuel innovation in the electronics industry.

“(With CHIPS), we are really trying to create a new way of designing chips,” DARPA’s Olofsson said. “We have to reinvent the ecosystem. We have to reinvent the way we design things. We have to invent manufacturing technologies.”

DARPA is working on several pieces of the puzzle to realize its goals, including formulating standards for chiplets to enable a plug-and-play model for the industry, devise faster SerDes technologies, and develop low-cost interposers/bridges for die-to-die interconnects. The agency also is looking to develop new pick-and-place systems, enabling chiplets to be placed on the package at high speeds.

Standards are key. “Once we have standards, you can imagine any vendor in the U.S. designing a number of chiplets and offering them for sale. So system integrators can build complex systems,” Olofsson said.

Fig. 5: DARPA’s vision of CHIPS Source: DARPA

CHIPS is making progress on the standards front. For its part, Intel is licensing its Advanced Interface Bus (AIB). The bus handles high-bandwidth, die-to-die communications in a package.

As part of CHIPS, Intel started the AIB Promoters Group, which will provide the technology royalty free. Over time, Intel plans to form a consortium for AIB.

For CHIPS, Intel is also offering its silicon bridge technology, which is an alternative to a silicon interposer. Intel’s technology, dubbed Embedded Multi-die Interconnect Bridge (EMIB), makes use of a piece of silicon that connects one chip to another in an IC package. In addition, members of CHIPS can also utilize traditional silicon interposers as well.

Fig. 6: EMIB implementation (silicon bridge). Source: Intel

The chiplet approach is promising. It might be the ultimate path toward heterogeneous integration. But if the pieces don’t fall into place, chiplets may end up being a niche or one of many forgotten technologies in the market.

Related Stories

The Case For Chiplets

Getting Serious About Chiplets

Chiplets Gaining Steam

DARPA CHIPS Program Pushes For Chiplets

Great article!

Citing this note from a recent Tom’s Hardware article on Intel’s Embedded Multi-Die Interconnect Bridge (EMIB) technology:

“Chiplets are a great idea, but a standardized SiP interface between components is important, especially if other companies are involved in the effort. The AIB and UIB interface IP blocks we see on the [Intel] Stratix 10 die are the key. UIB connections are a general-purpose SiP interface for HBM and ASICs, while AIB supports transceiver connections, [analog], and other general-purpose components.”