Nanosheets and nanowire FETs under development, but costs are skyrocketing. New packaging options could provide an alternative.

As several chipmakers ramp up their 10nm finFET processes, with 7nm just around the corner, R&D has begun for 5nm and beyond. In fact, some are already moving full speed ahead in the arena.

TSMC recently announced plans to build a new fab in Taiwan at a cost of $15.7 billion. The proposed fab is targeted to manufacture TSMC’s 5nm and 3nm processes, which are due out in 2020 and 2022, respectively. Other chipmakers, including GlobalFoundries, Intel and Samsung, also are looking at technologies for 5nm and beyond.

Both 5nm and 3nm present a multitude of unknowns and challenges. For one thing, the specs of these technologies are murky, if not confusing. And not all of the technologies are alike.

Regardless, based on the roadmaps from various chipmakers, continues to slow as process complexities and costs escalate at each node. The roadmaps, of course, could change. But for now, Intel plans to ramp up 10nm in the second half of 2017, with 7nm slated for production in early to mid-2020, according to industry sources. Intel’s 5nm production is targeted for early 2023, sources said, meaning its traditional 2-year process cadence is extending to roughly 2.5 to 3 years.

For now, Intel plans to extend the finFET to 7nm, sources added. In 2020, TSMC plans to ship 5nm, which is also expected to be a finFET. In reality, though, TSMC’s 5nm will likely be equivalent in terms of specs to Intel’s 7nm, analysts said.

Beyond 2020, however, the roadmap is uncertain. For this timeframe, chipmakers are evaluating several next-generation transistor types for a “true” or “full-scaled” 5nm technology. (TSMC may call it 3nm, but it’s closer in terms of specs to 5nm.)

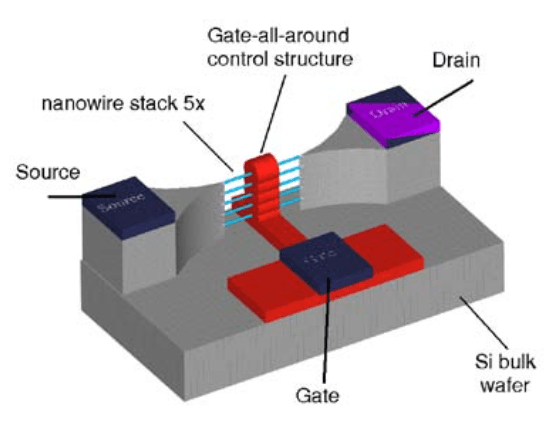

The leading transistor contenders for a full-scaled 5nm technology right now include finFETs with new materials, gate-all-around FETs, and a related technology called nanosheet FETs. Another viable option is to go vertical and adopt a 2.5D and/or a 3D packaging technology because there are several technical and economic roadblocks with classical IC scaling at 5nm and beyond. By then, IC scaling might be too expensive or could grind to a halt.

Fig. 1: Gate-all-around FET. Source: École Polytechnique Fédérale De Lausanne

Bob Johnson, an analyst at Gartner, said that the 5nm node will likely happen, but it won’t hit high-volume manufacturing until sometime after 2020.

But even if 5nm happens, it’s likely that only a few companies will be able to afford it. “It will be expensive,” Johnson said. “Manufacturing costs at 5nm will probably be 2.5 to 3 times more than at the 16nm/14nm generation. Design costs will continue to skyrocket. This will put fully integrated 5nm chips out of reach for a large number of consumer applications, and limit them to only the market segments demanding the highest levels of performance and (those) willing to pay for it.”

At 5nm, it will cost $500 million or more to design a complex system-on-a-chip (SoC), according to Gartner. In comparison, it will cost $271 million to design a 7nm SoC, roughly 9 times the cost for a 28nm planar device, according to Gartner.

It’s too early to say what will happen at the “full-scaled” 3nm node, which is nearly a decade away. For this, researchers are exploring several technologies. Nonetheless, given the enormous costs for these technologies, the question is clear: Why bother developing 5nm technology and beyond?

The industry, according to some, will require these advanced processes for use in future servers and mobile systems as a means to deal with a major onslaught of data hitting the market. “(There is) an explosion of data,” said An Steegen, executive vice president of semiconductor technology and systems at . “Many applications, such as social media, generate a lot of data. We have to make sure that we don’t end up in a data deluge. If we don’t provide technology and systems solutions for these technology platforms, you are going to end up with server farms the size of Manhattan.”

So how does the industry continue to scale? Semiconductor Engineering has taken a look at the technology options at these nodes, such as finFETs, nanowires and 2.5D/3D schemes.

Confusing nodes

Not everyone will move to advanced nodes, of course. Many will stay at 22nm and above. “Performance is important,” said Rajeev Rajan, vice president of marketing for IoT, automotive and new markets at GlobalFoundries, at a recent event. “But cost-effectiveness is also important.

And within those planar segments, the number of new applications continues to grow. “There is not just one driver of growth,” Rajan said. “There are a multitude of growth drivers.”

Walter Ng, vice president of business management at UMC, added: “There is handful of specific companies that are trying to drive the leading edge. We believe that there are still a lot companies that have not even entertained going onto finFETs, because it’s just too cost prohibitive.”

Only a select group of deep-pocketed chipmakers and foundry customers will pursue 10nm, 7nm, 5nm and perhaps beyond. But what exactly do these numbers mean.

For years, chipmakers followed the traditional transistor scaling metrics at each node. The idea is to scale or multiply the key transistor specs by roughly 0.7x at each node, which, in turn, will double the transistor density. In addition, chipmakers also strive to provide 20% more performance or a 40% power reduction at the same frequency at each node.

At 14nm, Intel followed the traditional path. In contrast, TSMC and others diverged from the norm. TSMC moved to finFETs at 16nm, but the specs, such as the contacted poly pitch (CPP) and the metal pitch, were more like 20nm. CPP, a key transistor metric, measures the distance between a source contact, the gate and a drain contact.

In effect, there are two different specs for nearly the same node number. Intel follows a full-node spec, while TSMC is a half-node (or more) behind. Chipmakers will follow the two divergent spec paths at 10nm and beyond, creating even more confusion in the market.

Today, Intel, Samsung and TSMC are in various stages of ramping up their 10nm finFET processes. Then, in 2017, TSMC will move into risk production with 7nm finFETs.

TSMC calls it 7nm, but the numbers don’t exactly correspond. “What others call ‘7nm’ is close to Intel’s 10nm in terms of density and performance,” said Mark Bohr, a senior fellow and director of process architecture and integration at Intel.

Based on those trends, TSMC’s 5nm will resemble Intel’s 7nm. And TSMC’s 3nm will look like Intel’s 5nm.

The confusion over the nodes is a minor issue, however. It pales in comparison to the technical and economic challenges in terms of moving to 5nm and beyond.

For example, Intel’s 14nm process consists of a CPP of 70nm and an interconnect pitch of 52nm. In comparison, a full-scaled 5nm technology is projected to have a CPP from 32nm to 42nm and a metal pitch of 24nm, according to the National University of Singapore (NUS). Then, at 3nm, the CPP is 20nm with a metal pitch of 18nm, according to NUS.

Extending the finFET

To reach those dimensions, chipmakers will require new and major breakthroughs in the fab. At 7nm and/or 5nm, for example, the industry wants extreme ultraviolet (EUV) lithography to help simplify the pattering flow. In addition, chipmakers will require new breakthroughs for the interconnects, the tiny wiring schemes in devices. And that’s just the tip of the iceberg.

The result is that IC manufacturing costs will be astronomical at 5nm and beyond. The solution? “The way you offset process costs is to scale faster,” said Aaron Thean, a professor of electrical and computer engineering at NUS. “You want to make more transistors per unit area.”

In fact, there are several ways to cram more transistors in smaller space with today’s finFETs, a move that will enable chipmakers to extend finFETs to 7nm and perhaps 5nm.

Introduced at 22nm and 16nm/14nm, finFETs are different than conventional planar devices. In finFETs, the control of the current is accomplished by implementing a gate on each of the three sides of a fin.

Here are some of the ways to extend the finFET:

• Reduce the number of fins on the transistor.

• Make the remaining fins taller.

• Add low-k and air spacers to the scheme.

• Introduce new channel materials.

One way to extend the finFET is to re-engineer the fin. Today’s 14nm finFET may consist of a 9-track standard cell with a total of four fins on the same transistor. Each fin has a height of roughly 50nm. By scaling at 7nm, a chipmaker could shrink the cell size from 9 to 6 tracks. The number of fins is reduced from four to two on the transistor, according to Thean. The height of each fin is 65nm to 70nm.

At 5nm, the cell is reduced from 6 to 5 tracks. It would consist of only one fin at a height of 90nm to 100nm. “I’m reducing the size of the cell, which is effectively scaling the area of the cell,” Thean said. “I have to make the fin taller just to provide enough drive current.”

A 5-track cell with one fin enables a CPP of 42nm and a metal pitch of 32nm, according to Imec. “This reduces area by 16% without pitch scaling, and provides 34% energy gain from 6T cells,” said M. Garcia Bardon, a researcher from Imec.

Taller fins, however, are subject to parasitic capacitance, which could impact the performance. Parasitic capacitance is unwanted capacitance that exists within the circuit elements. It can alter the ideal behavior of those elements.

To reduce the capacitance, the industry has proposed to insert low-k spacers into the finFET scheme. In another approach, IBM and GlobalFoundries have devised partial air gaps. An air gap would sit between the gate and the silicide metallization module in a finFET. “It is experimentally verified that the partial air spacer reduces the Cgs by 15% to 25% and the (effective capacitance) by 10% to 15% at 10nm ground rules,” said Kangguo Cheng of IBM Research.

In yet another challenge, silicon—the traditional channel material—won’t provide enough mobility. In response, Samsung recently demonstrated a 5nm finFET with a compressive strain of silicon germanium (SiGe) for pFET and a tensile silicon strain for nFET.

A strain-relaxed SiGe buffer layer is introduced as a buried stressor. “As a result, both tSi and cSiGe devices show a 40% and 10% electron and hole mobility gain over unstrained (silicon), respectively,” said Dong-il Bae, a principal engineer with Samsung.

So in theory, the finFET can be extended to 5nm, but there are still some issues here. One challenge at 5nm is keep the sub-threshold slope below 70-millivolts per decade. But maintaining the electrostatics and mobility of the device are easier said than done.

Going to nanowires

Once the fin width approaches or goes below 5nm, the device suffers from quantum confinement effects. As the fin becomes thinner, the bandgap goes up. The threshold voltage increases, prompting the device to break down.

That’s why the industry is looking at several next-generation transistor architectures at the 5nm full-scaled node. (As stated above, TSMC calls this 3nm, although it is closer to 5nm.)

Currently, the lateral gate-all-around FET and the nanosheet FET are gaining steam at 5nm. Other technologies, such as III-V finFETs, tunnel FETs and vertical nanowires, are not feasible today.

Gate-all-around FETs, sometimes called lateral nanowire FETs, are an evolution of finFETs. In gate-all-around the fin is made taller, then segmented into three or more nanowires.

Imec recently demonstrated gate-all-around FETs, based on vertically-stacked 8nm diameter nanowires. The nanowires are the channels. Then, a gate surrounds the nanowires on four sides.

“(With gate-all-around), you get the full wrap around and a little bit of electrostatic control,” said David Fried, chief technology officer at Coventor, in a recent interview. “Gate-all-around also says you will get some gate scaling.”

It also provides a slight performance boost over finFETs, but there are several challenges, namely drive current and parasitic capacitance.

The fin in the finFET has an ample surface area, which enables decent drive current. With gate-all-around, though, you have nanowires. So there is less surface area. “There is not enough drive strength per unit area, and even more importantly, the parasitics are too large relative to the conducting surface,” said Terence Hook, a senior technical staff member at IBM Research.

Parasitic capacitance is problematic at 5nm. It creates external resistance in various parts of the device. This includes the junction, the silicide Schottky barrier and the contact/viaO/M1 module, according to Reza Arghavani, a managing director at Lam Research. “Schottky barrier height could account for 32% degradation in the drive current,” Arghavani said.

To reduce parasitic capacitance, Leti and others have proposed the idea of introducing low-k spacers in gate-all-around. Then, to boost the performance, a SiGe compound is introduced into the pFET.

But is that enough? “My most general comment on GAA is that nanowires—be they vertically or laterally oriented—aren’t quite the right thing for a real technology,” IBM Research’s Hook said.

Recently, IBM Research proposed what it says is a more viable solution, a stacked nanosheet FET. Still in R&D, a nanosheet FET resembles a lateral nanowire FET. But in nanosheet FETs, the wires are much wider and thicker. “The sheets are just wires with a different aspect ratio,” Hook said, adding that nanosheet FETs provide better electrostatics and drive current.

Fig. 2: Cross-section simulation of (a) finFET, (b) nanowire, and (c) nanosheet. Source: IBM.

Both gate-all-around and nanosheet FETs are promising, but there are still some major gaps in bringing them from the lab to the fab. “With gate-all-around, you need certain capabilities,” said Raman Achutharaman, corporate vice president and general manager of the Etch Business Unit at Applied Materials. “All of the capabilities have to come together to make it work.”

There are other issues as well. “(Nanowire) technology could be pushed to 3nm,” said Marie Semeria, chief executive of Leti. “The question is the variability and the manufacturability of such a structure. The control of the technology is more and more important. We have to manage the stress in the process.”

Going vertical

If the industry fails to find a solution, there are other options. Instead of traditional scaling, the industry could go vertical. There are a number of 2.5D/3D options. For some time, the industry has been developing 2.5D stacked die using interposers and through-silicon vias (TSVs). Along these lines, Intel is pushing a technology it calls Embedded Multi-die Interconnect Bridge (EMIB). In EMIB, a package would consist of various chips. Tiny pieces of silicon at the die borders connect the chips in the package.

There are a number of new approaches, as well. For example, Leti is working on a monolithic 3D technology. For this, transistors are stacked on top of each other in a sequential process. The layers are connected using tiny vias. The challenge is to process the layers with minimal thermal impact.

Still in R&D, monolithic 3D is promising. “This could be relevant for heterogeneous integration of different functions—an analog function stacked on a digital function with a high-density interconnect,” Semeria said.

Leti and others are also exploring the concept of chiplets. Chiplets are discrete components of an SoC. But rather than putting everything on one die, they are developed separately for inclusion in a package. “With chiplets, you have the flexibility to choose the right (IP),” Semeria said. “You have more options with the partitioning.”

Time will tell what transistor and/or 2.5D/3D technology will prevail at 5nm and beyond. Indeed, there are too many unknowns in a challenging, if not chaotic, business environment.

Related Stories

What Transistors Will Look Like At 5nm

Will 5nm Happen?

Advanced Packaging Requires Better Yield

Making 2.5D, Fan-Outs Cheaper

10-20 nm space between Cu lines is practically 100% ReRAM risk.

Similar to Don Quixote, Sub 10nm processes are a Foundry’s windmills

The current fin height is closer to 40nm than to 50nm: https://en.wikichip.org/wiki/14_nm_lithography_process.

And good thing to keep clarifying that not all node ares created equal, and for introducing the full-scaled idea where you compare to Intel’s node, who has just kept scaling as usual at all nodes instead of renaming 20nm as 16nm after inserting FF. But this does make it confusing since traditionally you have more covered the foundries (TSMC, GloFo, SS). So when you talk about 5nm (e.g. “Parasitic capacitance is problematic at 5nm.”), do you mean the foundries’ 5nm node, which will have the feature sizes about the size of Intel’s 7nm, or Intel’s full-scaled 5nm node, which will have about the feature sizes of say TSMC’s 3nm node.

Great article for the rest, but are you sure about Intel 7nm being FinFET? It will, as you have said, be equivalent to TSMC’s 5nm node by then. And it will be their 4th gen finFET. No other technology since strained silicon at 90nm has had enough steam for more than 2 gens before needing *supplemental* technologies (90nm strained Si -> 45nm HKMG -> 22nm FF -> 10nm ??), and it’s only getting harder. So curious to see FF is surviving that long, but probably that has more to do with the alternatives have so many issues (horiz/vert GAA nanowires) or are that radically different so are even harder (tunneling FETs, spintronics, etc.).

But Bill Holt seemed to imply something else a few years ago. Sure it’s just a quote from an investor meeting to appease investors that Intel still has a mfg lead, but still, he seems to imply there will be big things beyond FF sooner rather than later.

https://twitter.com/witeken/status/807599016359981056

If they have nanowires with air spacing, do they need to check them for sensitivity to gravity and acceleration?