Developers must integrate interface IP that’s optimized for power, cost and time-to-market.

The low-cost smartphone segment is fueling the growth of the overall smartphone market. Smartphones are being adopted in emerging markets and are displacing feature or basic phones in developed markets. Mobile phone device manufacturers are closing the leadership gap with the No. 1 vendor – Samsung – by competing in both the high-end and low-end smartphone segments. See Table 1.

Table 1: Top Five Smartphone Vendors, Shipments, Market Share and Year-Over-Year Growth, Q3 2014 Preliminary Data (Units in Millions) Source: IDC Worldwide Quarterly Mobile Phone Tracker, Oct. 29, 2014

Device manufacturers have to deliver cost-effective smartphones with satisfactory feature-sets that are one or two tiers below their flagship smartphone products. For example, high-quality front and back cameras, as well as a high-resolution display, are key features users expect to see in their low-cost smartphones.

As a result, low-cost smartphone device manufacturers must invest in system integration to reduce hardware cost. The typical bill of materials (BOM) includes an integrated application processor with baseband capabilities and peripheral components such as two image sensors, display module, non-volatile memory (NVM) and LPDDR volatile memory. The BOM cost can be reduced by lowering the application processor cost, which is determined by the silicon, fabrication, packaging, test and operational costs.

Application processor providers are now asked to integrate as many system components as required in a smartphone and build an optimized system-on-chip (SoC) for a sub-segment of the low-cost smartphone market within a specific price range.

Even a low-cost smartphone must have a high-resolution display, a high-resolution image sensor for the back camera and a lower-resolution image sensor for the front camera. (See Figure 1 below) Image sensors and display resolutions can be targeted to slightly different smartphone price points, which means the display and camera connectivity needs to provide flexible and standard interfaces that accommodate a variety of performance levels. It is imperative to integrate the latest interface IP optimized for power, cost and time-to-market.

Figure 1: Application processor servicing Smartphone employing two image sensor interfaces and one display interface

Camera and display interface protocols

The MIPI Alliance Camera Serial Interface-2 (CSI-2) and Display Serial Interface (DSI) protocols are based on the MIPI D-PHY, which is the physical layer used for MIPI CSI-2 and DSI applications connecting image sensors and displays to SoCs in mobile and embedded applications. The MIPI protocols are widely used in mobile devices, providing a flexible and cost-effective solution for the low-cost smartphone segment. They are designed and optimized to meet the required features of image sensors and display applications, while minimizing cost and power consumption. The D-PHY economically implements the high- and low-speed traffic by connecting to the protocol layer via the PHY-Protocol Interface (PPI) connectivity.

Figure 2: MIPI Camera Serial Interface (CSI-2)

CSI-2, seen in Figure 2, is a high-performance serial interconnect bus that connects camera sensors to digital imaging modules, such as a host processor or an image processor. CSI-2 utilizes MIPI D-PHY for the physical layer and high-speed differential interfaces with several data lanes (typically 1, 2, 4 or even 8) and a common differential clock lane. It supports host and device interfaces needed in the application processor, camera sensor and bridging applications.

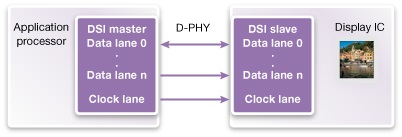

Figure 3: MIPI Display Serial Interface

The Display Serial Interface (DSI) seen in Figure 3 is a high-speed, high-resolution serial interconnect bus that offers connectivity to display devices. DSI uses a MIPI standard D-PHY for physical layer high-speed differential interfaces with up to four data lanes and a common differential clock lane. Pixel data and commands are serialized into a single physical stream, and status can be read back from the display. The protocol supports host and device interfaces needed in the application processor, display panel and bridging applications. It also supports display devices operating in video mode and command mode, as the need for more complex and lower-power implementation is dependent on the system implementation and application.

Because the connection is source-synchronous, the clock is provided from one side of the link (called the Master) and isn’t embedded with the data. The data rate can be determined based on the specific available data stream and it’s not fixed to a certain speed. This configuration simplifies circuit design because complex clock and data recovery (CDR) circuitry isn’t needed at the receiving end. Unlike other SerDes architectures that use data encoding, the D-PHY doesn’t require a byte-oriented coding scheme and its data doesn’t carry an overhead.

Driving higher data rates

Most available image and display sensors in the market today support high-speed burst modes of up to 1000 Mbits/s per each lane. The target is to add bandwidth with the same number of pads.

The recently released MIPI Alliance D-PHY v1.2 specification extends the capabilities of D-PHY high-speed burst to 2.5 Gbits/s per lane, enabling displays and image sensor developers to support aggregated bandwidth of up to 10 Gbits/s using four data lanes, or 20 Gbits/s using eight data lanes with slight modifications.

Driving lower power consumption

The D-PHY’s scalability helps save power. It uses a selectable number of data lanes and shuts down unused data lanes. In most cases, data lanes are operated in the unidirectional mode for high-speed transmissions, where a Master D-PHY and Slave D-PHY source and receive the clock, respectively. For example, a DSI Host application implemented on the SoC side employs a Master D-PHY to source the signal to the display on the board, while a CSI-2 Host application uses a Slave D-PHY to receive the signal from the image sensor.

Because the D-PHY isn’t bound to specific rates, it can optimize power consumption based on the traffic generated when sourcing a clock signal that corresponds to the actual required data rate. This flexibility creates a cost-effective solution by removing the need for unnecessary memory buffering and design complexity. In addition, the D-PHY supports high- and low-speed (or low-power) operations. High-speed transmission uses the clock lane, while low-power operation utilizes the self-clocked data to save power, while the clock lane stays idle.

Driving lower costs

The MIPI D-PHY v1.2 specification includes throughput enhancements for higher bandwidth image and display sensors, but it also helps in reducing cost.

The ability to send the same amount of data in fewer data lanes contributes to reduced silicon area and fewer pins which directly relates to application processor silicon cost. The application processor that needs to interface with an image-sensor at 4 Gbits/s can use two data lanes operating at 2.0 Gbits/s instead of four lanes at 1.0 Gbit/s. When this lane and pin reduction methodology is used with several image sensors, it leads to significant silicon and package cost savings.

Summary

Synopsys’ DesignWare MIPI IP has enabled many SoC developers to reach production using D-PHY, CSI-2 and DSI IP. The DesignWare MIPI D-PHY v1.2 IP dramatically reduces area, cost and power. The IP minimizes time-to-market and maximizes ROI with its configurability options and variety of solutions for CSI-2 and DSI applications, reducing the number of SoC designs required to support multiple applications.

For more information about Synopsys DesignWare MIPI IP, visit: http://www.synopsys.com/mipi

Additional Resources

• Synopsys’ New DesignWare MIPI D-PHY Cuts Area and Power by 50 Percent

• Leadcore Achieves First-Pass Silicon Success on Smartphone Application Processor with DesignWare MIPI IP

• MIPI Alliance Introduces MIPI C-PHY Specification and Updates its D-PHY and M-PHY Specifications

Leave a Reply