A new packaging format provides extreme silicon area density versus package volume.

In the world of solid-state memory fabs, bits per mm2 rule. In the memory packaging market, mm2 of silicon per a given package thickness is the defining feature. Both the memory architecture of the wafer and the package technology take advantage of 3D structures to achieve best in class bit density. In the case of the wafer fab, 3D NAND and other technologies are pushing the envelope to meet ever increasing storage needs by stacking memory cells on top of one another. In the memory packaging market, the industry typically stacks individual die on top of one another within the package. The higher the number of stacked die equates to more memory cells in each package. The current state of the art is 16 die in a 1.2-mm package, but there is a constant need to reduce package thickness. To meet further reductions in memory package thickness, new approaches are needed to allow a large silicon area in a small volumetric space.

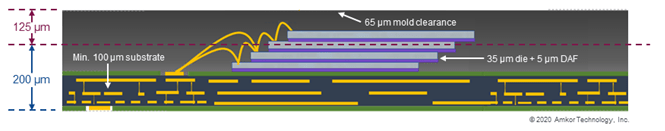

This blog post will demonstrate a new packaging format that provides extreme silicon area density versus package volume. The development explains how to vertically stack four wire-bonded die in a package with overall package thickness of 200 microns. The development involved four fundamental building blocks to achieve the goal of 200µ total package thickness.

Since the silicon wafers must be extremely thin, it was determined that an advanced wafer thinning process using stealth dicing before grind (SDBG) would provide the best chance to achieve the desired thickness. In the design, a total Si thickness of 25µ is needed, and SDBG was used to thin the Si wafer to the required thickness.

Fig. 1: SDBG process description for thin die.

Next, a unique design and bonding structure was used to allow the overall package thickness to be less than 200µ. If a traditional methodology was used, the minimum thickness would be 325µ total. While thinning the die + thin Die Attach Film (DAF) and low loop bonding would help, the total thickness would not be achieved.

Fig. 2: Traditional Stacked Chip Scale Package (SCSP) compared to the 200µ goal.

Thirdly, a novel die attach method was used on the new design format. This method takes advantage of a release technology like those used in panel and strip-level manufacturing and allowed the elimination of wasted space in the z-direction.

Fig. 3: Thin QDP and PiP design concept.

The development team focused on a Quad Die Package (QDP) design where the die is positioned in a cavity, rather than on a substrate. This allowed a more traditional wirebond structure, freedom to route signals to one or both sides in a Package-in-Package (PiP) structure and meet the 200µ goal. Manufacturing this design would require a temporary bond to a carrier and eventual removal of the carrier for the final product. The design avoided the need for low loop bonding and allowed the use of a multi-layered laminate substrate as an interconnect to the outside of the package.

Fig. 4: Thin QDP process flow.

Lastly, simulation was used to determine how to manage package warpage for such a thin design and identified the features needed to remain within useable targets. The simulation results influenced the design of the package and substrate to maintain warpage to levels of similar sized packages in high-volume production.

Fig. 5: Unit warpage of Thin QDP with and without adjusted mold volume.

In the initial proof of concept build, it was discovered that the warpage of the package was far greater that the thickness of the package. This would lead to inevitable issues with placement, adhesion, and testing of the unit.

Fig. 6: Results of simulation models.

Based on these results, the development team performed finite element analysis (FEA) to determine that the warpage was a function of epoxy molding compound (EMC) volume and silicon volume within the package. Since the mold volume and Si volume are inversely related (increasing one reduces the other), the model showed a balance wherein warpage can be decreased to levels acceptable in other memory products.

Fig. 7: Test structure for adjusted mold volume.

Fig. 8: Warpage results before and after mold volume adjustment.

The four facets of the development were confirmed using functional silicon and were electrically, mechanically, and environmentally tested in component level reliability testing. Amkor believes that this package provides a leap forward in accommodating high silicon density in a thin package. The ability to provide a 200µ package with a four die stack will help meet the demands for smaller/thinner mobile devices, provide freedom in designing groups of packages to meet the memory needs of the system, and lead to other adaptations that can take advantage of extremely tight z-height restrictions.

Fig. 9: Reliability performance of thin QDP.

This development demonstrates how the limits of Stacked CSP packaging can be pushed to make a 200µ QDP using a unique architecture and release process obtained from experience in wafer level packaging. In this way, it has been shown that 3D packaging need not involve Through Silicon Via (TSV), flip chip, or complex assembly techniques to achieve extremely dense Si area within a given package volume.

Leave a Reply