Technology is still a long way from being commercialized, but it points to some interesting new possibilities.

Research is underway to develop a new type of logic device, called non-volatile logic (NVL), based on ferroelectric FETs.

FeFETs have been a topic of high interest at recent industry conferences, but the overwhelming focus has been using them in memory arrays. The memory bit cell, however, is simply a transistor that can store a state. That can be leveraged in other applications.

“Non-volatile devices (like FeFETs) will enable many applications if they can be integrated with a standard CMOS process cost-effectively,” said Sagheer Ahmad, senior director of architecture at Xilinx. “Non-volatile logic can be used for some of the same applications where embedded FPGAs are used in ASICs. It also can enable valuable customization of security embedded in the chips, like root-of-trust security.”

NVL is a generic notion and is not bound to any specific technology. “What you’re looking for in this situation is the electrical equivalent of a mechanical switch,” said Rob Aitken, fellow and director of technology on the research team at Arm. “You flip it, and then it stays flipped.”

While the notion of being able to store a logic state in a transistor sounds simple, a harder look starts to raise questions about what the FeFET is storing. There are lots of ideas on how to use these transistors, some of which even veer into analog territory. Do any of them lead to NVL?

FeFET basics

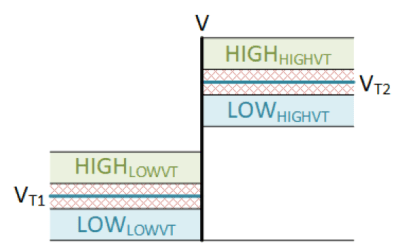

FeFETs have a ferroelectric material as the gate (or in addition to a standard gate). That means that this layer, if configured or programmed correctly, will have an electric dipole. Depending on the direction, that dipole will either add to or subtract from the intrinsic threshold voltage of the transistor.

Fig. 1: The ferroelectric material will add to or subtract from the intrinsic transistor threshold, giving two threshold options. Source: Bryon Moyer/Semiconductor Engineering

“You’ve got this ability to switch between two different threshold voltages,” said Lucian Shifren, vice president of research at Cerfe Labs. “The difference between those threshold voltages is your memory window,” referring to the difference between two memory states.

Even having to think about thresholds is foreign to designers, who are accustomed to logic in the abstract. As Aitken described, “[Using FeFETs for NVL] involves dealing with a bunch of problems with actual devices, like, ‘What voltage are they running at? What’s their VT? How did it get programmed? Why does it flip when you flip the signal, but it doesn’t flip when you turn it off?’”

The challenge is to go from this low level of abstraction back up to a logical level — potentially one that’s different from the way we think about logic today.

Simple use: saving state

One obvious application of NVL is to save a snapshot of the state of a circuit. That snapshot will survive a power down, potentially enabling quicker recovery because the state can be restored rather than being re-computed.

Today, this role is played by so-called “balloon latches.” These are registers that are powered externally by a battery (or some other source). By loading the balloon registers, they can survive the loss of power. The obvious cost of doing this is the need for the extra battery, which will need to be periodically changed (or recharged). NVL would make such a battery unnecessary, saving cost and simplifying system maintenance over time.

This can also simplify sleep management. “[The system] has to know that the amount of power that it’s going to save [while asleep] is worth it,” explained Aitken, referring to the typical overhead of putting a system to sleep and then reawakening. “If you had this other methodology, you could take little tiny sleeps and potentially save some energy.”

Is the FeFET going to give us this conceptually simple capability? While it seems obvious that a transistor with storage would be able to store its state, note that what’s programmed in the FeFET isn’t its output state: It’s the threshold. The output state then depends both on the inputs and the threshold. That’s not captured by storing a threshold state unless you have a feedback circuit that takes the output and forces a threshold change that would guarantee that output state on power-up.

This tension between the notions of state and threshold adds some complexity, as further analysis suggests.

Playing with two thresholds

At its simplest, we’re looking at a transistor that can have one of two threshold voltages. That can complicate the standard way we think about logic.

“Even if the devices worked ideally, you’d still have to rethink how you did a lot of logic,” noted Aitken. Our notions of logic are dominated by Boolean algebra, which posits two states — true and false. A standard inverter adjudicates an input by measuring whether the signal is above or below the threshold, giving the necessary two states.

But if we can have one of two thresholds, then things aren’t so clear – and it depends on where the thresholds lie and what signal levels are selected. It helps to think of two logic regimes: a higher one and a lower one. The higher one assumes the higher VT; the lower one assumes the lower VT. For each of these, we have a logic high and a logic low. That gives us four logic states: high high (logic high for a high VT), high low, low high, and low low.

Fig. 2: There are four logic levels, two of which correspond to the low-threshold state, with the other two corresponding to the high-threshold state. Source: Bryon Moyer/Semiconductor Engineering

In one case, we could have two thresholds with overlapping high and low input ranges – ones that went to the rails in the way we’re accustomed to. One could imagine this being useful as a performance tweak. For operations that don’t require the highest performance, a higher VT could be selected, slowing things somewhat while lowering leakage current.

Fig. 3: The two thresholds are close enough that their ranges overlap. Source: Bryon Moyer/Semiconductor Engineering

This could be dynamically changed for a burst of activity, as long as the programming time is low enough to be useful. It’s like another way of implementing dynamic voltage/frequency scaling (DVFS). “I can either have a transistor that’s going to leak like crazy, or I can have a transistor that leaks less and has lower drive current,” said Cerfe Labs’ Shifren. But this isn’t really a logic function. It’s a performance function.

Multi-level logic?

Alternatively, the logic levels could be separated, such that the high low is above the low high. For this scenario, the inputs could not operate at the rails in all cases, complicating voltage generation. This could also be used for performance tuning, but it raises a question about whether there’s utility in having two non-overlapping logic regimes.

Fig. 4: If separated further, the two thresholds could establish two separate sets of high and low levels that don’t overlap, effectively giving two completely separate operating regimes. Source: Bryon Moyer/Semiconductor Engineering

Unlike the overlapping case, where you operate in one of two modes, each of which has only two levels, here you could operate with all four levels. This opens up the possibility of using quaternary logic instead of binary logic. Because the ranges don’t overlap, there’s no ambiguity in noise-free signals.

What about the outputs?

Exactly how the inputs will interact with the thresholds is an interesting question in its own right, but it raises many other practical questions, not the least of which is that a standard inverter – with standard or ferroelectric gate – will generate a binary output. And yet we’re driving it with four levels. That’s fine on the input side, but if this is going to drive another similar gate, then how do we derive the appropriate output voltages?

Here again we have two possibilities. If we have overlapping ranges, then we need to have a way to adjust the output levels to conform to one of the modes. If all transistors operate in the same mode, this effectively means level-shifting all of the outputs. If different transistors can have different modes, then you need to be sure that the output voltages being generated conform to the input levels of the next transistors.

Fig. 5: An inverter (shown here as a block, since there may be some level-shifting circuitry in there) must generate the appropriate voltages for the next stage to read. The input band defines the range for the input in a non-overlapping case. That may make the output levels different from the input levels. Source: Bryon Moyer/Semiconductor Engineering

That would mean a transistor operating in one mode for the inputs, but potentially generating outputs for a different mode. It therefore would not be so meaningful to say which mode the entire transistor is operating in.

In addition, if the output was driving more than one transistor, and the driven transistors weren’t all in the same state, things become less meaningful absent level shifters on every line (rather than simply on the output of the inverter).

Fig. 6: A single inverter driving two different inverters in different modes would need to generate two separate sets of outputs. Source: Bryon Moyer/Semiconductor Engineering

For non-overlapping ranges, with quaternary logic, it’s no longer a matter of generating a level-shifted version of high and low. Now one needs to generate one of four separate levels, and that’s not obvious for an inverter. The very idea of inversion becomes unclear for quaternary logic because there is no simple notion of “opposite state.”

More complex logic becomes even more convoluted, suggesting that for this to be a useful mode, a new algebra would be needed as an underpinning to circuit development. That new algebra could inform a completely new set of gates that operate with four levels. Is this perhaps more consistent with a future non-volatile computing theory?

What about programming the state of the transistor?

Finally, one must be able to change the state of the transistor. This means effectively programming or erasing the transistor using a high or negative voltage pulse. That creates the need for yet another two voltage levels on the input signals.

Those voltages would have to remain out of reach for normal logic, but still remain within reach of the voltages on the chip. “The minute you introduce higher logic voltages, it means you have to have higher programming voltages,” observed Shifren. “You can actually have logic disturb issues.”

For the non-overlapping model, that would mean six possible voltages to choose from — four for operation plus two more for changing state. There may be a way to split the gate and have the programming voltages on a different signal, which would simplify the logic signals at the expense of extra programming signals. But it would have to be done carefully to ensure that the input gates physically felt the micro-domains that were changed by the programming gates.

Fig. 7: A full system may need as many as six levels: two each for the two modes (for four total), plus two programming levels. Source: Bryon Moyer/Semiconductor Engineering

The timing for changing state also would be important, which could restrict the semantics of such reprogramming. If reconfiguration was very slow, then many quick, reactive changes would not be possible. Changing state would have to be done as a matter of a slower overall reconfiguration of some sort.

If state changes could be done quickly, on the other hand – on the order of general logic delays (say, a few nanoseconds on today’s technology), then the number of ways to use this could increase. That said, however, exactly what things might be useful have not been established.

Having looked at these details, the question remains: Is this non-volatile logic? It’s interesting logic, perhaps. New things might be possible, but they’d have to be powerful enough to merit extra circuitry to manage all the levels. Still, does that make it non-volatile logic in the way that people think it might?

What gets lost in the conversations is that, in all of these cases, what we’re storing is the threshold, not the actual signal state. It would take more circuitry to interpret the threshold as a state that can be correlated with the output of a circuit. Otherwise, what’s being stored is a configuration, not necessarily the actual state.

Conquering digital design

Today’s designers use abstraction to create enormous quantities of logic. No one has to think through exactly what the thresholds are when designing digital circuits. RTL and PDKs abstracts those details away. The challenge is that these details are front and center with FeFETs. “What we’re looking for in FeFET space are basic architectures that allow you to maintain that abstraction,” said Aitken.

“You want to be able to hide all the nasty stuff somehow,” he continued. “In an ideal device, it would be hidden below the logical operating layer. You’d say, ‘Oh, here’s this thing, it’s a NAND gate or an inverter or something. And I want it to take the state of the logic that it has now. And then, when I power it off, I just want it to stay there.’ That is potentially going to blow up a whole lot of what we do now in RTL.”

The first question is whether we’re truly dealing with NVL. If we are, then we need to establish a uniform set of abstractions that allows designers to implement these new circuits quickly, efficiently, and in the volumes necessary for practical circuits.

“Ideally, we’d like to create CMOS-like gates that don’t have clocks or reset signals that don’t have some kind of function that says, ‘store/don’t store,’” said Aitken. “In practice, we may not be able to do that.”

Then there are things that feel more like analog

Other possible uses come to mind for a transistor with a programmable threshold. While they don’t fall under the category of non-volatile logic, discussions that start with logic often end up here.

There’s a general question of whether analog functions could be improved by a ferroelectric transistor as a component. While that question has by no means been answered, there are some very specific things that one can imagine doing with a FeFET. “If FeFETs work, then they would enable a bunch of the analog things that have so far failed,” said Aitken.

One use might be for filtering noisy signals. One could imagine adjusting the threshold of the transistor to block spurious parts of the signal. That could be a way of personalizing the circuit early on to deal well with a specific environment, or it could be a dynamic process that adjusts as noise comes and goes.

Fig. 8: Thresholds could be dynamically adjusted slightly to account for noise on input signals. Source: Bryon Moyer/Semiconductor Engineering

Implementation, of course, is not at all clear. How long is the feedback path? Who’s making the decisions, and how long does adaptation take? How many extra transistors are needed for all of that?

Another use could be in stacking FeFETs with gradually increasing thresholds for use as an ADC generating something like thermometer code. Presumably, the programming of these thresholds would be a power-up calibration step rather than an ongoing dynamic process (although the latter would be possible).

Fig. 9: Multiple transistors with gradually increasing thresholds could theoretically act as an ADC. Voltages within the noise margin of a transistor may cause issues as a practical consideration. Source: Bryon Moyer/Semiconductor Engineering

The idea here is that a voltage is presented to multiple FeFETs in parallel. That voltage would be below the threshold of some and above the threshold of others. Where that break occurred would then give a digital result.

Using FeFETs for neuromorphic computing has definitely been identified as a promising idea. Neuromorphic networks may implement something called an integrate-and-fire circuit. The fact that repeated, limited programming spikes might hit the gate, gradually changing the threshold, makes this feel like it’s integrating that input. Exactly what constitutes “firing” remains unclear.

Keeping the “logic” in “non-volatile logic”

The possibilities of FeFETs are fascinating to consider. But go too far down that rabbit-hole, and questions and complications accumulate. It’s clear that many notions we take for granted today would require some rethinking.

What appears to be missing is a well-accepted description of what NVL means. What would computing be like in such a situation? Shifren, for example, believes that it would move us away from a von Neumann computing model.

“We have been stuck in von Neumann and binary volatile logic for 45+ years, including vacuum tubes and BJTs (bipolar junction transistors),” he said. “It’s not just the switch that needs a refresh. It is top to bottom. However, without the switch there is no reason for a refresh. FeFETs bring in some form of NVL, but what is that NVL? Is NVL intrinsically better for low-power? Is it better for high performance? No one knows.”

Leave a Reply