Hard IP could reduce time and cost for heterogeneous designs, but there are still challenges to solve.

Building chips from pre-verified chiplets is beginning to gain traction as a way of cutting costs and reducing time to market for heterogeneous designs.

The chiplet concept has been on the drawing board for some time, but it has been viewed more as a possible future direction than a necessary solution. That perception is beginning to change as complexity rises, particularly at advanced nodes, and as new markets open up that require semi-customized solutions.

This approach also could help re-populate the industry with startups, where mask costs at 10/7nm are well beyond the reach of small companies. Startups always have been a driver of innovation, but the number of new companies has dwindled as capitalization requirements rise. And with more chipmakers demanding that IP be silicon-proven, the number of startups has plummeted.

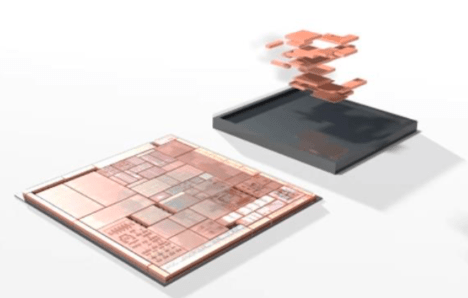

That could change in the near future, particularly as the U.S. Department of Defense’s DARPA branch rolls out its Common Heterogeneous Integration and IP Reuse Strategies (CHIPS) program. DARPA’s plan is to bring various IP blocks, subsystems, or even chips together on an interposer in a 2.5D-like package.

While this is critical for designs used in the military, Dan Green, program manager for the CHIPS program at DARPA, said the goal is to extend this type of integration and modular design into other markets. “It’s really about enabling the broader community to embrace the ecosystem, and we’ve seen a lot of openness to that. We’ve had conversations with the large players in the space. There is an appetite to understand how to overcome the challenges of design and high NRE for circuit design particularly as you move to the expense of these advanced nodes.”

Fig. 1: DARPA’s CHIPS concept. Source: DARPA

In many respects, chiplets are a logical evolutionary step for IP. Ty Garibay, CTO of ArterisIP, points to two main benefits—being able to create smaller footprint devices with dramatic increases in yield, and process optimization per function.

But it’s also starting off in a new direction, and there are always growing pains when it comes to technology.

“The SoC design play is a behemoth,” said John Ferguson, product marketing director at Mentor, a Siemens Business. “It is very frightening for a company to move away to a multi-die strategy simply because of the huge infrastructure that has grown to support the design flow. A big part of this is the design kit, but a design kit alone is not sufficient. The foundries and third parties also supply pre-verified and pre-characterized IP. An SoC designer can purchase or access these to include in their design and be 100% confident they will work, so long as they integrate it per the requirements.”

Using a chiplet approach ultimately would make this even simpler.

“The designer could focus on design at a higher level and integrate known and trusted functionalities,” Ferguson said. “If you think about it, today system companies already do something like this. They are not selling a chip in a package. They are selling a solution. That solution may have lots of chips included in various approaches into a single component. Examples include automotive, aerospace, and smart cities.”

Pros and cons

There are still some unknowns with this approach, however. For example, how does a chiplet manufacturer ensure a component is robust? And if a known good die (KGD) is put into a package, how do you pinpoint and test for a manufacturing defect that might cause the entire device to fail?

But the benefits are significant if this approach goes mainstream.

Hugh Durdan, vice president of strategy and products at eSilicon, has seen the dynamics first hand as part of the evaluation of a project that involved chiplets. “The reason why we were interested in chiplets was we needed a piece of IP which was either not readily available to license, or if it was available, was not mature enough to feel comfortable with integrating into the core ASIC. In this case it was a high speed SerDes. What we looked at was an alternative to a monolithic design with the SerDes integrated right with the ASIC, and instead consider a chiplet approach where we would purchase the chiplet from a third party, design on the ASIC an interface that talked between the ASIC and the chiplet, and then we would integrate it all together into a multi-chip module for the package.”

From an economics point of view, the chiplet approach showed a fairly significant benefit on the development cost, Durdan said, mainly because the cost to license the chip-to-chip interconnect between the ASIC and the chiplet was a lot less expensive than the IP in the chiplet. “Also, it was a lot simpler to integrate than the SerDes would have been because the interface isn’t as high-speed, and it’s a bit simpler than the chip-to-chip interface. From a partitioning point of view, it moved some of the logic that would have been in the ASIC, as it was already in the chiplet, so it made the ASIC itself a little bit simpler.”

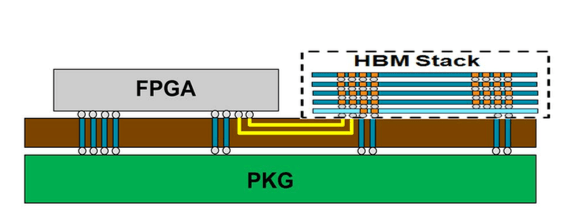

Total savings would have been millions of dollars in development cost, he said. And even though packaging is more challenging for chiplets, what has eased concerns with this type of approach is that technologies like HBM are starting to take off. “2.5D assembly technology has become mature enough,” he noted. “It’s still challenging, but people have successfully gotten into high volume production with it. So a lot of the early concerns have gone away.”

Fig. 2: 2.5D schematic. Source: Xilinx

ArterisIP’s Garibay believes a great deal of potential resides within technological approaches such as these. “Within a few years there will be active substrates in 22nm or 20nm, or maybe even 16nm that have both logic and chiplet-to-chiplet routing, along with essentially flip-chip sockets on active substrates that would have footprints for either a standard socket — which is the nirvana of the future — or a less-standard socket that allows for each chiplet to be designed and manufactured in the semiconductor process that is best suited for it.”

However, there are still challenges to be overcome for how exactly the chiplets talk with one another, as well as with other components in the system, as well as with the system itself.

Garibay isn’t aware of a technology that could fit the bill entirely here today, but one of the ways the substrate could be implemented is that the chiplet could be primarily be the network-on-chip realized in another, cheaper, coarser technology. And while this may be a valid use, it may only be practical for the biggest players. This is a straightforward use of the technology, where 7nm chiplets of CPUs or small clusters of CPUs could be created and seated into uniform sockets on a substrate, and that would fundamentally be a cost play if the yield wasn’t there at 7nm.

At least a half-dozen companies are working on a variety of interposers and bridge technology, which is less expensive than an interposer. Intel already has its EMIB, and Samsung has announced an RDL bridge for wafer-level packaging. Multiple industry sources say others are under development, which will lower the cost significantly.

Chiplets work well with any of these approaches. “In its fullest incarnation, the beauty of the chiplet concept is that I can put the L3 cache on the substrate so that I’m not burning square millimeters of 7nm stuff on worthless RAM,” Garibay said. “Just pack it with CPUs and let the RAM live below, and I can pack the substrate with SerDes. It was brutally difficult to implement SerDes in 14nm. It’s going to be more so in 7nm. It’s hard to see how traditional analog SerDes functions at 7nm. And then there is the sheer expense of trying to do super high-performance analog in 7nm where the point of the game is iteration. You might have to take four shots at it, and when you are taking four shots at a $5 million to $10 million mask set, that’s probably not a great idea. So if you can put those SerDes on a new variant process that is much more hospitable to high-speed analog simply because of the nature of the planar device itself, and you could have a wider variety of devices because masks and mask sets in that process are so much cheaper, then you could have a two analog solution, a fat analog one, a thick oxide one, a super thin oxide. These are all the variants that analog guys want. They could turn out great analog very quickly and the cost of doing the package implementation of the chiplet becomes amortized over mask reductions, time to market, and reductions in manpower.”

Commercialization

Getting this ready for commercial applications is a non-trivial amount of work, however.

“How long is it going to take to commercialize it?” asked Ravi Ravikumar, director of strategic alliances at NetSpeed Systems. “There is a lot of development that needs to happen. We are talking about ease of use and things like that. I don’t have to tell you how IPs and reuse have done over the years. It’s proven for the SoC market that use of IPs and reuse have enabled effective design methodologies, have enabled people to create advanced designs in a much faster timeframe, and for domain-specific applications. You can take an IP and put it together for a mobile application, or take the same thing and apply it for some other application in a slightly different way or by putting a couple of other IPs together, so it’s almost like a platform where you pick different blocks and put it together. The concept of chiplets — and specifically the DARPA CHIPS program — is to develop a new technological framework in which different functionalities and blocks of IP can be segregated into small chiplets, which can then be mixed, matched and combined onto an interposer. You’re talking 2.5D designs here—almost like joining pieces of a jigsaw puzzle. It’s a great concept, but it takes time because there are a lot of issues that need to be worked out.”

However, if a standard physical footprint could be assumed, that would go a long way toward making this a viable strategy.

“There could be a quick-turn design ASIC, where you’d start with a chiplet of an FPGA with that footprint and then very quickly Open-Silicon or eSilcon could flip it to a much smaller chiplet of ASIC logic with that dedicated footprint,” Garibay said. “I don’t have to change my underlying substrate die that has all the cool analog. I don’t have to requalify it. I just reduce the net silicon cost, and I’m able to swap out that accelerator potentially, if we postulated that’s a form of an accelerator for data processing or AI or a database accelerator. I’m able to swap that out at manufacturing time to meet market segment needs with a substrate that’s common. You could almost see a new market there of some of these system integrators being able to pervade the substrate die and enable startups to create chiplets without having to gain the expertise to implement the full chip. How much innovation could we unlock if we had functionally the equivalent of a VME card definition, and now all I have to figure out is how to build the chip that went into the VME card, not the entire VME card? Now we’re so dramatically reducing the design problem that I could see many more people being able to bring real innovation to silicon.”

Next steps

How smooth the road forward will be remains to be seen. Some of the biggest companies in the industry, which could benefit from the chiplet approach, also may want to protect their positions in the industry. Still, DARPA’s involvement could help increase competition even if the entrenched players may wish that is not the case.

“The people that have the most to win in the chiplet area are the ones that would build a super huge 7nm or 5nm chiplet, anyway, because that’s what they do,” said Garibay. “If the chiplet approach works, they may be able to do it at a dramatically reduced production cost even if they have to give away a little performance. Then, if the technology exists, TSMC will make it available to other people and you’ll see a proliferation of flexibility of design. If you put ‘this chiplet’ and ‘this chiplet’ down, it will work. If you put this other one down, it will look bad and your friends will make fun of you.”

At the end of the day, this is potentially energizing for the industry where a lot of what has happened over the years — consolidation of suppliers, dramatic increases in manufacturing costs, increased design complexity driving up design cost, consolidation of customers, giving customers more control over pricing. “It’s been exciting in a bad way for small players. Finally, there is something that is actually energizing to the industry in a way that might grow the pool instead of convincing young people that it would be better to go do an app for Facebook,” Garibay said.

Mentor’s Ferguson agreed that a chiplet approach represents a potentially new era for design. “Instead of a designer focusing on a chip to be used in a specific set-top-box, which they then have to hope competes well against other set-top boxes, they now can design a chip that could be ported into say any infotainment system. Now they have opened up their potential market significantly.”

Related Stories

Making 2.5D, Fan-Outs Cheaper

Standards, new materials and different approaches are under development to drive 2.5D, 3D-ICs and fan-outs into the mainstream.

The Chiplet Option

More companies are assessing pre-built and pre-verified circuits as a way of reducing time to market.

DARPA CHIPS Program Pushes For Chiplets

The U.S. government takes its own approach to heterogenous integration.

The Week In Review: Manufacturing

Making chiplets; 5G; tax reform; TowerJazz China fab.

Leave a Reply