Market for advanced packaging begins to diverge based on performance and price.

Two years ago, at the annual IMAPS conference on 2.5D and 3D chip packaging, the presentations were dominated by talk of fan-out wafer-level packaging. There was almost no talk of through-silicon vias, which previously had been heralded as vital to 2.5D and 3DIC packaging.

Fast forward to this month’s 3D Architectures for Heterogeneous Integration and Packaging conference in Burlingame, Calif., and while FO-WLP still dominated, TSVs were included a number of presentations. As advanced packaging begins to mature, packaging is beginning to bifurcate between those applications requiring faster time to market with lots of different kinds of components, which is where fan-out shines, and those requiring blazing fast speed, which is where TSV-based solutions are essential.

Fig. 1: TSV wafer starts, 2013-2021. Source: Yole Développement

FO-WLP really started kicking into gear in 2015 after it was revealed that Apple used the packaging approach in its A9 application processors, which went into that year’s iPhone. Apple utilized TSMC’s Integrated Fan-Out (InFO) packaging technology.

FO-WLP is preferred for mobile electronics. But TSV-based 2.5D and 3D packaging is finding a market in areas such as networking, cloud-based server chips, and increasingly in designs for artificial intelligence and virtual/augmented reality. There are other types of packaging that are being developed and explored by the industry, as well, but these two technologies are the ones mostly being found in high-volume manufacturing of advanced chips.

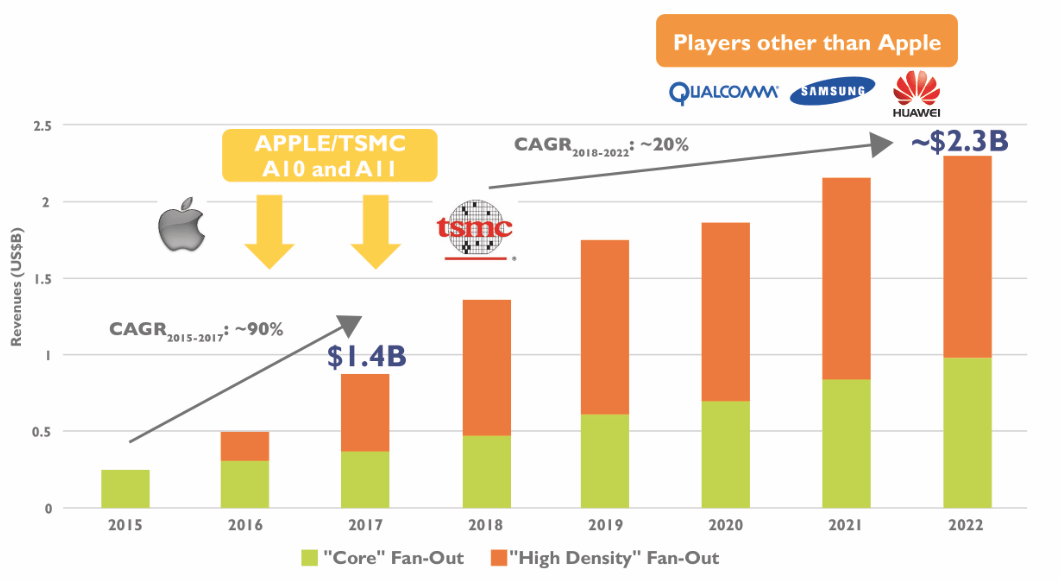

Fig. 2: Fan-out revenue by market type. Source: Yole Développement

There also is something of a middle ground emerging between these two worlds, driven largely by efforts to circumvent the high cost of TSV-based silicon interposers. Intel is touting use of its Embedded Multi-Die Interconnect Bridge (EMIB) as a less expensive and faster alternative to interposers. Samsung also has its own as-yet unnamed version of a bridge, which connects die through the redistribution layer. And several other companies are developing bridge technologies, as well, according to industry sources.

Fig. 3: Intel’s EMIB. Source: Intel

New drivers for packaging

Behind these advances in packaging are some new drivers for multi-chip solutions, notably connected vehicles, smart cities and smart homes, according to Jim Walker, a consultant at WLP Concepts.

‘You’ve got a lot of semiconductors that are going to go into these systems – LiDAR, radar type of systems, and communications, with all of these various devices, whether there’s traffic signals or what have you, but also the electrification of the powertrain,” he said at 3D ASIP. “Security is going to become a big deal with autonomous driving.”

He also pointed to smart city and smart home technology as significant growth areas.

“The smart city encompasses smart utilities, smart homes, citizen responses, emergency response, the whole transportation system, green planning, and green living. Street lighting is a big one that has taken off already. There’s a lot of semiconductors that are being looked at and used in all of these applications. The diversification of usage of semiconductors is becoming much more prevalent, especially this year, as all these new applications now are starting to introduce them, and that’s why you’re seeing this 20% growth,” Walker said. “The smart home – thermostats, lights, electric vehicle charging, EV charging, a lot of entertainment – we already have that occurring. Looking at home health care and remote monitoring – instead of going to the doctor, a lot of health maintenance companies talk about setting up to remotely monitor and at least the initial diagnosis, we do it from home, and based upon talking or interfacing with the doctor, or based on some remote monitoring system that you might have at home, be it blood pressure or heartbeat, that will interface with the doctor, and you can decide whether the doctor needs to have you come in, and do an in-person type of exam.”

Behind that growth, though, is a need for a faster and more flexible wafer fabrication process. This is what’s driving interest from these market segments in advanced packaging.

“The time for turning around a new type of product, and new wafers, and getting the wafers verified, and the circuitry verified, is generally a 12- to 18-month cycle time, from the time we design to the time we really have that wafer going into high-volume production,” Walker said. “As we know, we come out with new-model cellphones every three to six months. If it takes 12 to 18 months to really get a new chip going, that doesn’t really make it compatible. The chip is kind of antique by the time it comes out. We also need a more adaptable system integration process through packaging and our board-level assembly process, and the buzzword has been heterogeneous integration for the past year or two. Of course, we want it at the lowest cost possible. Do we integrate via silicon? Do we really continue on Moore’s Law every 18 to 24 months, and shrink the process nodes and everything else? Design costs are rising. Higher silicon costs have been shown at 10nm and 7nm. The actual cost of the silicon is going up for each of the chips. In addition to that, we’ve got higher test costs, yields are a factor, so we need more flexibility in wafer fabs to meet that time-to-market, and more customized processes.”

System-in-package technology can speed up the design and manufacturing of new chips, while offering lower costs than system-on-a-chip device technology, he noted. The lines between chip fabrication, packaging, and board-level assembly are blurring in the interest of faster introduction for products.

The Apple Watch is an example of how foundries and OSATs can take the lead in integrating nearly 100 components in a product that has an extremely limited, tight form factor, Walker said. ASE and TSMC were deeply involved in realizing what Apple wanted for the wearable gadget.

In a dozen sessions over three days, 3D ASIP dealt with multiple topics in IC packaging, such as microbumps, high-density interconnect bonding, advanced materials, substrate build-up and thin-wafer handling, application-specific intellectual property, the Defense Advanced Research Projects Agency’s CHIPS program, and image sensors.

Fan-outs

Fan-outs are improving in performance, as well. Vinayak Pandey, director of product and technology marketing for STATS ChipPAC, cited the key driver for this packaging approach as system integration of multiple dies, particularly for 5G wireless communications, millimeter-wave technology, and photonics.

“What’s happening in 5G? Power dissipation, power efficiency need to be optimized, and integration needs to be managed,” Pandey said. “On the front end, it becomes more complicated. And then on the mobile side, form factor and cost are two big things today. We do see an improvement in electrical performance as we go into higher frequencies.”

Pandey noted that reducing surface roughness in packaging substrates becomes a factor as frequencies climb to 60 gigahertz, 77GHz and higher levels. “There is definitely a performance enhancement, in addition to form-factor improvements, particularly at high frequency and millimeter-wave [with embedded wafer-level ball grid array packaging],” he said.

There has been a lot of experimentation in fan-outs over the past few years. Fan-outs come in a number of different flavors, such as chip first and chip last, and the packaging can include everything from wafer-level to panel-level.

“Fan-out means a lot of different things to different packaging technologies,” said Ron Huemoeller, vice president of corporate research and development at Amkor Technology. “If you look at what’s happening in the industry today, fan-out happens on many levels. Let’s just talk about redistribution, because that’s essentially what fan-out is. It’s redistributing I/O for communication, for different components and dialogue. You have it at the board level, the substrate level, the OSAT level, which is where wafer-level fan-out comes into play, and the foundry level, which is restricted down below 1 micron to more thick and organic technologies. So that’s the first step. It’s redistribution, and at what level are you going to redistribute your technology for communication.”

A second factor involves the scale at which the packaging is done. “You have RDL first, then you have packaging second,” Huemoeller said. “Most packaging happens at the strip level, or single-unit level. And to be honest, in the packaging world, there’s really no such thing as single-unit packaging. It’s really strip level, wafer level, or eventually panel level. Those are different ways you can package your technologies today, and there are different costs associated with doing each of these package-scale technologies. This battle has been waged for a long time, especially with the introduction of wafer-scale packaging. So whether you know it or not, package technology has been shifting back and forth between wafer-level fan-out and flip-chip CSP for the last five or six years.”

That shift has been driven by cost. “Performance is the same, one versus the other,” he said. “It becomes an economic issue for our customers — which one provides the best cost to them at that time — and they toggle back and forth. We’ve seen PMICs bounce back and forth between wafer-level fan-out and flip-chip CSP the last four or five years. And it continues. If you look forward into the decisions of what’s going to be packaged in which manner and which scale packaging, it comes down to what type of RDL do you need, and then economics of packaging – what can provide the lowest cost as a final packaged product.”

Conclusion

The number of packaging options continues to grow, but the advanced packaging world is beginning to splinter around two key drivers—performance in markets where cost is not the primary motivation, and time to market and heterogeneity in markets where cost is one of the top considerations, if not the main consideration.

Whether these two worlds merge, or whether they continue to split further apart, remains to be seen. There are efforts to improve the performance of fan-outs, and there are likewise efforts to reduce the cost of through-silicon via technologies such as silicon interposers. Advanced packaging is just beginning to gain its footing, and it will likely look very different over the next couple of years as new approaches are developed and refined to handle huge increases in data from a variety of sensors, particularly streaming video, as well as to provide the speed necessary to handle next-generation applications such as artificial intelligence, hyperscale computing, industrial and regular IoT and 5G.

Leave a Reply