Glass, aluminum and other options and issues in 3D integration.

Unable to scale horizontally, due to a combination of lithography delays and power constraints, manufacturers are stacking devices vertically.

This has become essential as the proliferation of mobile devices drives demand for smaller circuit footprints, but the transition isn’t always straightforward. Three-dimensional integration schemes take many forms, depending on the required interconnect density. Image sensors and high-density memories might stack one chip directly on top of another, connected by through-silicon vias, while a system-in-package design might place several sensors and their controlling logic on a single redistribution layer.

For designers, the key question is not how to physically contain individual dice, but how to integrate a complex system, according to Thomas Uhrmann, EV Group’s director of business development. Still, all forms of 3D integration — from relatively low-density fan-out wafer level packaging to high-density chip stacks — share some challenging assembly problems.

First, in order to ensure consistent mechanical and electrical connections, and facilitate any further lithography steps, each wafer and each redistribution layer or other element in a complex stack should be planarized. This can be accomplished by polishing, by depositing a dielectric or adhesive on top of existing topography, or both.

Second, silicon, metal interconnects, and auxiliary materials like adhesives can have very different coefficients of thermal expansion. The assembly process must control stress and warpage to ensure reliable connections in the final package. The package design might, for example, incorporate compliant materials that can accommodate process-induced stress. Alternatively, it might reduce stress by limiting high temperature processing. For example, an adhesive that can be applied and cured at room temperature will contribute less stress to the system than one that requires elevated temperatures.

Finally, assembly involves precise handling and alignment of individual dice, of wafers reconstituted from singulated dice, and of thinned wafers with exposed through-silicon vias. Processing steps may involve both the front and back sides of the wafer. In the finished package, for example, a die might rest on top of and connect to a redistribution layer through TSVs, while the active layer is bonded face-to-face or face-to-back to another die.

The exact process sequence varies, but wafers typically must be bonded to and debonded from one or more temporary carrier substrates. In work presented at last year’s IEEE Electronic Components and Technology Conference, Shelly Fowler, principal application engineer in Brewer Science’s WLP Materials Division, observed that wafer flips are common. A front-attached carrier allows thinning and other backside processing before transferring the wafer to a back-attached carrier for further front-side processing.

Transporting the wafer, front side up and back side up

As a result, inexpensive and reusable wafer carriers, and robust, removable adhesive layers are fundamental elements of advanced assembly processes. The first 3D integration schemes used steel carriers that were mechanically and chemically robust, and able to tolerate annealing, solder reflow, and other thermal processes.

More recently, glass has emerged as the material of choice. It facilitates alignment from the carrier side and allows the use of laser debonding methods (discussed below). Uhrmann pointed out, however, that wafer detection and alignment systems that depend on light or shadowing may need to be reworked to accommodate glass carriers. A full process line might require a substantial number of changes.

Whichever carrier is chosen, the bonding adhesive is usually spin-coated, then cured. The front side of the wafer might need a relatively thick layer to planarize existing topography and protect the circuit components. On the backside, Fowler said, planarization is less necessary and a thinner layer might be less prone to bowing. The specific choice of adhesive depends on the debonding method to be used. There are four possibilities — chemical, thermal, mechanical, and laser debonding.

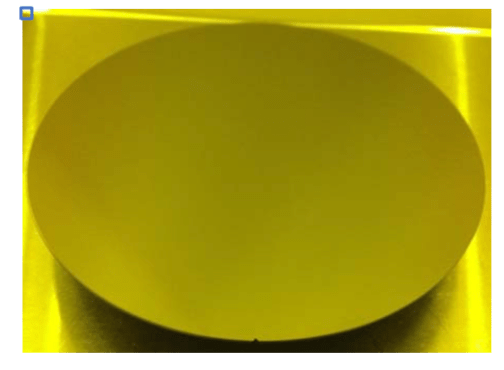

Fig. 1: Silicon wafer bonded to glass carrier. Source: Brewer Science

Debonding pros and cons

In chemical debonding, an appropriate solvent dissolves the adhesive, floating the wafer free from the carrier. This method is slow for large wafers, as the solvent can only reach the adhesive from the edges of the wafer. Chuan-An Cheng, while studying for a Master’s Degree at Taiwan’s National Chiao Tung University (he is currently a mechanical engineer at Garmin Corp.), discovered that while debonding can take place at low temperatures, finding an adhesive that will tolerate the necessary process solvents can be difficult.

Alternatively, thermal debonding heats the adhesive until it softens enough for the wafer to slide off. This method is fast, simple, and inexpensive, but only suitable for packaging schemes with modest temperature requirements. None of the processes applied to the carrier/wafer combination can exceed the softening temperature of the adhesive. Usually, this excludes solder reflow and heat-driven permanent bonding steps. On the other hand, low temperature processes that are compatible with thermal adhesives are less likely to bow or warp the substrate.

Mechanical debonding also offers a relatively narrow process window, EV Group’s Uhrmann said. The adhesive must be strong enough to survive subsequent process steps without slippage or delamination, but weak enough to allow easy separation from the carrier when desired. This method is most commonly used for highly standardized products like stacked memories. It is generally not suitable for applications with a wide mix of package components.

Finally, laser debonding is emerging as a cost-effective and versatile solution. Light shining through a transparent carrier decomposes the bonding material, causing the bond to fail. Laser debonding is attractive in part because of its digital character. The adhesive is permanent until the laser decomposes it completely.

When more than one of these options can be used, cost is usually the deciding factor. The cost of a debonding process depends on its throughput and the amount of energy — whether supplied by heat, light, or a mechanical tool — needed to drive the process. Mechanical debonding might require less energy than thermal debonding, for example, but be slower than laser debonding. Any additional steps needed to remove adhesive residue will also contribute to the total cost.

What about the adhesive?

Chemical and thermal debonding typically use a single layer adhesive, which also serves as a compliance layer, planarizing the bonded surface of the wafer and accommodating any thermal expansion mismatch between the wafer and the carrier. This material must be able to tolerate whatever process steps the wafer will see. Delamination, whether due to stress or chemical decomposition, can cause local deformation of the wafer, misalignment, and other issues. After debonding, the adhesive should be cleanly removable without leaving residue on either the wafer or the carrier.

Mechanical and laser debonding, in contrast, frequently use a dual layer temporary adhesive. The first layer, applied to the wafer, is a planarizing adhesive. It’s thermally stable and protects the device features during processing. The second layer, in contact with the carrier, is a release layer. In laser debonding, the laser decomposes the release layer without affecting the adhesive, which can be removed by conventional de-taping methods. Chia-Hsin Lee, regional account manager at Brewer, and his colleagues found that a thin titanium/copper layer on the glass carrier facilitated debonding by reflecting scattered light back into the release layer. Cheng observed “snowflake” bonding defects when the adhesive curing temperature was too high. These defects appear to occur if a pocket within the adhesive layer decomposes, producing gases that can push the release layer aside. If the adhesive contacts the carrier directly, the debonding laser will be unable to release that area.

In mechanical debonding, the debonding tool initiates a split between the adhesive and release layers — “like between two pieces of Velcro,” as Uhrmann described it. The debonding front propagates along the clearly defined interface between the two materials. It’s possible to apply mechanical debonding methods to single layer adhesives, though, as Seiya Masuda, operation manager at FujiFilm, and his colleagues demonstrated at last year’s IEEE Electronics Packaging Technology Conference.

Bonds that don’t break

While bonding a wafer to a carrier for handling purposes depends on removable adhesives, the bonds between components of the package must be permanent, providing robust electrical, thermal, and mechanical connections. Depending on the packaging scheme, permanent bonding might involve either complete wafers or singulated dice, connected either to other wafers or to redistribution layers or interposers. Wafer-to-wafer bonding is preferable to chip-to-chip or chip-to-wafer bonding because it offers high throughput and simplifies alignment between the layers of the structure.

Generally speaking, the bonding surfaces need to be planar and clean. Topography can cause voids or misalignment, while adhesive residue and metallic oxides can degrade electrical conductivity. At this year’s IEEE Electronic Components and Technology Conference, researchers at IHP Microelectronics demonstrated aluminum-to-aluminum thermo-compression bonding. Aluminum metallization is appealing because of its compatibility with CMOS processes, but surface roughness and rapid oxidation are significant obstacles. The IHP group used a vacuum bonding process, etching the bond pads to produce a clean surface. They achieved a strong bond with 60 kN of pressure at 300°C, well below the 500°C limit for CMOS compatibility.

Wafer bonding processes based on copper metallization can use BEOL inlaid copper damascene methods to form the bond pads. Either the dielectric must resist diffusion — BCB resin, for instance — or a separate diffusion barrier, typically SiC, is needed. While CMP is a well-established and mature process for BEOL metallization, wafer-to-wafer bonding can present dramatic topography variations with scribe lanes and large copper bond pads. Moreover, the wafers being bonded might come from completely different fabs, with different processes and specifications. The package assembly process must be able to account for these variations. Uhrmann described a hybrid bonding process developed in collaboration with Imec. It depends on van der Waals forces to draw the two wafers together, facilitated by a thin layer of moisture at the interface. Heating the combined stack expands the copper, completing the bond. Because the copper expands while the dielectric does not, perfect planarization is not necessary.

Bonding and metallization

While this article looks at permanent wafer bonding in isolation, it is closely related to the intra-package metallization. Solder bumps, copper pillars, and redistribution layers, among other options, all pose unique bonding problems.

Related Stories

Leave a Reply