Devices are still experimental, but they could solve power issues in scaling.

One of the main obstacles to continued transistor scaling is power consumption. As gate length decreases, the sub-threshold swing (SS) — the gate voltage required to change the drain current by one order of magnitude — increases.

As Qin Zhang, Wei Zhao, and Alan Seabaugh of Notre Dame explained in 2006, SS faces a theoretical minimum of 60 mV/decade at room temperature in conventional MOSFETs. This limitation has helped to drive interest in tunneling field effect transistors (TFETs), among other alternative designs.

In a TFET, a thin dielectric layer rather than a conventional channel lies between the source and drain. The applied gate voltage controls the overlap between the valence band of the material on one side of the dielectric, and the conduction band of the material on the other side.

In the “off” state, there is no overlap and no current flows. In the “on” state, the gate bias pulls the valence band on one side up to the level of the conduction band on the other side. The overlap allows carriers to tunnel through the dielectric barrier, and current can flow. This band-to-band tunneling mechanism also acts as an energy filter, blocking high energy “hot carriers.” By reducing the leakage current in the off state, TFETs seek to reduce the SS necessary to achieve a desired on/off current ratio.

Building TFETs with low SS and enough tunneling current is not easy, though. Last year, Redwan Sajjad and colleagues at MIT showed that defects at the interfaces adjacent to the dielectric, and in the dielectric itself, can allow trap-assisted tunneling and contribute to off-state leakage current. In many devices, a strong temperature dependence of SS suggests that trapping and de-trapping of carriers — a thermally activated process — and the resulting trap-assisted tunneling may overwhelm the desired band-to-band tunneling.

Defects are especially problematic in materials other than silicon. Silicon has achieved its dominance of the integrated circuit industry in part because manufacturers can consistently produce high-quality silicon interfaces. Unfortunately, silicon has a relatively wide, indirect band gap, leading to a low tunneling probability and low drain current. Semiconductors with narrower band gaps, such as germanium and III-V compounds like InAs, also have much less mature manufacturing processes. TFETs based on III-V semiconductors may need 40 to 100X lower trap density relative to the current state of the art in order to achieve a reasonable “on/off” current ratio with steep subthreshold swing.

Multiple TFET designs

Against this background, papers presented at the IEEE Electron Device Meeting (IEDM) in December proposed a number of different TFET designs and compositions. One approach, discussed by Rahul Pandey (formerly Penn State, now an Intel device engineer) in a collaboration with IMEC, TSMC, and others, used a Ge/GeSn heterostructure to reduce the effective band gap while controlling leakage at the drain junction. The effective band gap can be reduced by either reducing the conduction band energy or increasing the valence band energy.

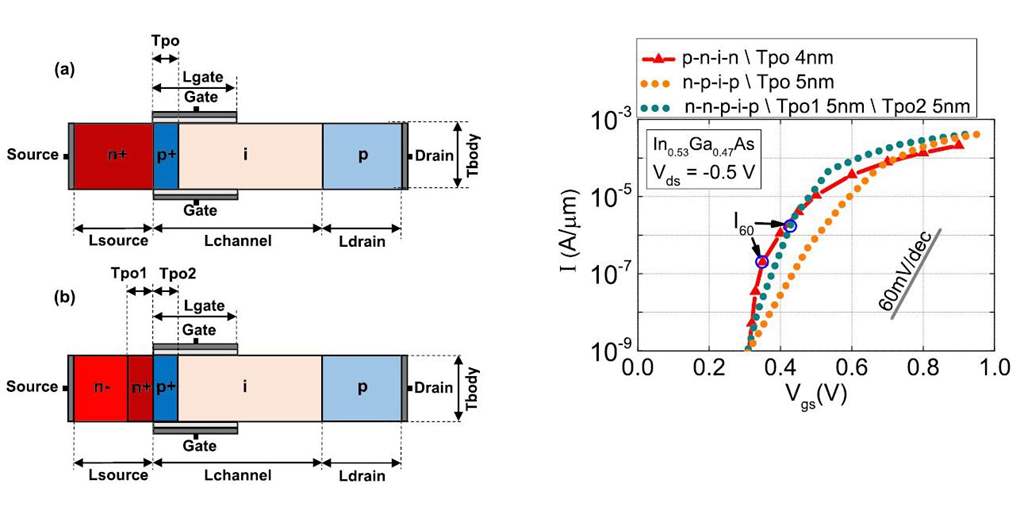

Fig. 1: TFET structure and performance. Source: IMEC

For example, In-based semiconductors reduce the conduction band energy, while Ge- and Sb-based materials raise the valence band. Thus, one common design uses an InGaAs/GaAsSb structure. Increasing the indium content in InGaAs decreases the band gap, but reducing indium suppresses leakage current. To balance the two objectives, this group found that a quantum well with increased indium only at the tunneling point gave the best combination of low band gap and low leakage. Nonetheless, state of the art Ge/GeSn devices had a 10X lower density of interface traps, improving both on current and SS.

Another approach depends on vertical nanowires. Researchers at Lund University grew nanowires from gold seed particles, deposited on a silicon wafer with an InAs layer. MOVPE growth produces wires with InAs/GaAsSb/GaSb segments. Sn and Zn are added to the precursor gases for n- and p-doping of the InAs and GaSb regions, respectively. The exact composition of the central “channel” segment is unknown. After deposition, etching reduced the wire diameter before integration of an HfO2-based gate-all-around gate stack. While very high quality nanowires are possible, the very small dimensions of these structures mean that transport occurs by discrete steps, rather than as a uniform flow in a continuous band structure. Single traps can have a substantial effect on overall device properties. These devices achieved SS of 48mV/dec, with an on-state current of 10.6 microamps/micron at the lowest SS. This exceeds best-in-class MOSFET performance at low voltage.

In light of the issues posed by the small tunneling area in a nanowire, Huili Grace Sing’s group at Cornell University seeks to take advantage of the uniform properties of 2-D materials such as metal selenides. These materials allow researchers to experiment with the thinnest possible layers and offer a choice of band gaps and band alignments. The Cornell group describes their device as a two-dimensional heterojunction interlayer (Thin) TFET, with a van der Waals barrier between WSe2 and SnSe2. Current flows out of the plane of the semiconductors, rather than laterally as in a planar transistor. This structure offers a relatively large tunneling area, making individual defects less important.

Yet another TFET design seeks to reduce leakage by placing phase change materials in series with the TFET. When the phase change material — VO2 in this work — is in the resistive state, little current reaches the transistor. When the VO2 is in the conductive state, the transistor is on.

The transition point depends on the properties of VO2, which changes from insulator to metal at 68°C. VO2 was chosen for its high contrast in conductivity between the two states, and the ability to induce phase change by electrical excitation. Two-terminal VO2 devices have been thoroughly characterized.

If VO2 is in series with the TFET gate node, the phase transition drives a steep increase in current through the TFET. These devices have good characteristics, but need high current at the gate to drive the VO2 transition.

Placing the VO2 element in series with the TFET source node may be more appropriate for low-power designs. As the off-state gate voltage increases, leakage current is limited by the insulating oxide until the power density triggers the phase change.

As the diversity of proposed devices shows, TFETs are extremely immature, experimental devices at this time. Nonetheless, even these preliminary results suggest that they may offer the industry a way out of its power consumption dilemma.

Related Stories

Pathfinding Beyond FinFETs

What structures and materials will be needed at 5nm and beyond.

What’s Next For Transistors

New FETs, qubits, neuromorphic approaches, and advanced packaging.

Tunnel FETs Emerge In Scaling Race (Nov 2013)

With voltages possibly below 0.5 volts, TFETs are a serious contender for ultra low-power applications at 5nm.

One-On-One: Aaron Thean (Jan 2015)

Imec’s process technology and logic devices guru talks about 7nm and 5nm parasitics, new materials and transistors, and where are the biggest unknowns.

What’s After CMOS? (Jan 2014)

There are more than 20 possible successors; carbon nanotubes, graphene and 3D devices are way down on the list.

Leave a Reply