Coventor’s CTO looks at new types of transistors, the expanding number of challenges at future process nodes, and the state of semiconductor development in China.

David Fried, chief technology officer at Coventor, sat down with Semiconductor Engineering to discuss the IC industry, China, scaling, transistors and process technology. What follows are excerpts of that conversation.

SE: In a recent roundtable discussion you talked about some of the big challenges facing the IC industry. One of your big concerns involves the uncertainties in terms of technology drivers that will propel future IC scaling. It’s unclear what will drive 7nm and 5nm. Can you elaborate?

Fried: We rode the CPU market. CPUs really drove a lot of logic technology scaling. And then all of a sudden, mobile kicked in and mobile really drove technology scaling for a number of years. Right now, on the memory side, the same few things drove DRAM. But now, with NAND flash, you are seeing just a ton of applications driving dense, cheap nonvolatile memory. Everyone has a lot of memory in their phones. The amount of memory is just unbelievable. Those are the commercial or consumer product waves that drove scaling and technology. The product-level drivers for memory scaling are very consistent going forward. Everyone needs more memory in a smaller form factor. Video bandwidth is going up and you have 8K. So memory demand for scaling is significantly healthier. The logic demand for scaling is tough to figure out. I am not saying it’s not there. I am saying CPU and mobile might not be as intense as it was when it was driving us up the curve. So what is it that will drive scaling? It’s not IoT. IoT doesn’t drive advanced scaling technology. IoT drives derivative technologies. It drives older and more mature amortized fabs, but IoT in and of itself doesn’t drive the most advanced technologies. So is it GPUs, gaming and virtual reality? Maybe VR becomes a commercial success in a product-level driver. VR will drive CPU development and display technology. There are those things out there. But it’s unclear what to bet on.

SE: China is another hot topic in the IC industry. The nation is spending billions of dollars in the IC arena and building several new fabs. What’s your take on China?

Fried: If China is not already, they are getting to be one of the leaders in the consumption of semiconductor products. But they still produce less than 5% of the world’s semiconductor products. What is happening is that China is bringing their capabilities and capacity up fast. And they are just bringing a lot of the consumption home.

SE: China has nearly two dozen new fab projects in the works. Is there a danger of having too much fab capacity?

Fried: Basically, China does have an ‘if you build it, they will come’ situation right now. If they add 20% more capacity, it will be full overnight. If they add 200% capacity, it would be full overnight, because they just have the consumption to drive the internal manufacturing demand. That in itself is not driving advanced technology. It’s driving capacity. So they want to bring some production home. It’s probably going to suck some products out of other international facilities. But to be honest, who is putting up fabs in China? It’s many of the international companies. They are just starting to produce this stuff domestically.

SE: SMIC is developing 14nm finFETs with plans to ship them by 2020 or sooner. Can China get finFETs out the door?

Fried: Is this stuff easy? No, it’s not easy. Can they put together a 14nm finFET technology at some point? Yes, of course, they can. They are very smart people. Do they need to do this on TSMC’s schedule? No, they are so far behind that schedule. That schedule doesn’t matter to them.

SE: What else?

Fried: Remember what China is trying to solve. They are solving a consumption problem. They are solving a capacity problem. They are not sitting around and saying: ‘If I can only do 7nm, we would be out of this problem.’ That’s not the problem for them. Right now, the problem is they don’t want to make this stuff in another country.

SE: Let’s move to the technology. The foundries are moving to 10nm and 7nm finFET technology. Of course, the node designations are confusing and not all 10nm and 7nm technologies are alike. But what can you say about 10nm and 7nm?

Fried: 10nm is tough, and 7nm is tougher. 14nm, 10nm and 7nm are a relatively evolutionary scaling path. 14nm, 10nm and 7nm are, ‘Make it smaller and fix what’s broke.’ I oversimplify it when I say, ‘Fix what’s broke.’ There is a lot of engineering here. There are a lot of new processes, new deposition techniques, new etch controls and new lithography schemes. So there is a lot to that. But it’s relatively evolutionary from a device perspective.

SE: What’s the biggest challenge at 10nm and 7nm?

Fried: The middle-of-line interconnect is the battleground right now. Middle-of-line is really hard. It has the dimensional constraints of both the front-end and backend. It has the material constraints of the front-end. It has the design freedom that neither the front-end or backend have, so there are more shapes and constructs to manage than anything else. We saw that difficulty at 22nm. It got bad at 14nm. At 10nm, it’s just almost devastating. And then we are going to do 7nm.

SE: Can you describe the middle-of-line (MOL)?

Fried: You have to get the connections from the lowest levels of interconnects to the transistors. So there is some metallization and then there are contact schemes. And then there are all sorts of different and interesting designs. Do I contact the gate? Do I contact the source/drain? Do I contact both? Do I fly over the gate? There are all sorts of very intricate design constructs that have to be managed. It’s incredibly complicated. There is a lot of topology involved. It has to be very low resistance.

SE: Will we see material changes like cobalt in the MOL?

Fried: In the middle-of-line, the classic stack is a tungsten fill. The first liner is titanium, then titanium nitride and the tungsten fill. The big thing you have to remember is that it’s not just tungsten. There are liner films, as well. It’s not just what material you fill with. If going to a different material allows you to do some new void-free filling, and it allows you to get rid of one of those liner films, that’s a huge win. So it’s not just, ‘Can you fill better using some materials?’ It’s also, ‘Can I reduce the liners required because I changed my materials?’ There is a plausible scenario where you move from tungsten to a material that is fundamentally a higher resistance, but you are able to get a better fill and you lose less area and the liners. So the stud resistance actually improves. In addition, cobalt has been thrown around by a lot of people and a lot people are trying it. We haven’t used cobalt fill in manufacturing. Nobody has made that public yet.

SE: Then, of course, the industry continues to face challenges in the backend-of-the-line (BEOL, where the tiny interconnects are made). Any thoughts?

Fried: When you get into the backend-of-the-line, it’s tantalum, tantalum nitride and copper. The backend-of- the-line is not getting any easier. The challenges are a little different. It doesn’t quite have the same topological challenges as the middle-of-line, but you need to repeat the process over and over again. Your problems multiply as you go up. Also, the backend has to be very low temperature. The materials, such as dielectrics, have to be porous to be low-k. Basically, you are building a house of cards in soft materials.

SE: Do you expect to see a shift in materials in the BEOL?

Fried: A lot of these material changes will occur in the next node or two, say at 7nm or 5nm. I would love to see cobalt or ruthenium. I am not confident enough about any of it to put money behind it. Cobalt is getting there. The liners are interesting in both BEOL and MOL. Figuring out the liners is really tricky stuff. We’ve been on those classic schemes for so many years. We’ve known that you have to stop moisture ingress. You must have a barrier for electromigration. These liners and barriers provide a lot of key constructs in the structure. You would love to get rid of them, but you can’t. As you go to these new material systems, and we try to eliminate and optimize liners, there is going to be a lot of learning there.

Fig. 1: FEOL, BEOL. Source: Wikipedia

SE: How long will the finFET last and what’s next? Is that the gate-all-around or nanowire FET?

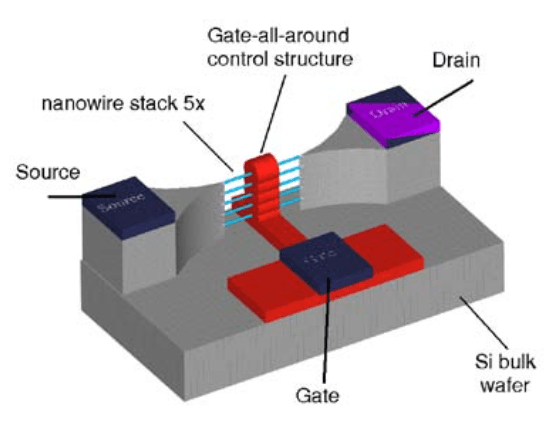

Fried: My suspicion is that 7nm looks pretty evolutionary. It will be finFET. If we see a change beyond finFET, it could be at 5nm. But remember, a lateral gate-all-around nanowire device is like a finFET with two extra etches. Going from a finFET to a lateral gate-all-around nanowire device is pretty evolutionary. I hope we start seeing that at 5nm. Beyond that, we don’t have much visibility.

SE: What does gate-all-around FET buy you?

Fried: All it lets you do is make a device with a shorter gate length. And a shorter gate length lets you fit in a tighter pitch. That’s it. The device, from a current perspective, has high resistance. It’s got parasitics. It’s not a great performance device, but it lets you scale.

Fig. 2: Gate-all-around FET. Source: École Polytechnique Fédérale De Lausanne

SE: Is that enough and is it cost-effective?

Fried: It’s cost-effective if it lets you scale enough. If you take several nanometers off the gate length, it lets you fit in a pitch where we can scale the front-end, get 2D scaling, and start to get 1.8x chips per wafer relative to the previous technology. Then it will make sense. It will be cost-effective.

SE: What are the manufacturing gaps for gate-all-around?

Fried: If the wafer is really planar, planar processing is relatively easy. You look down at the wafer. You use etch and deposition. FinFET brought some challenges to the floor that were already out there, where you have to care about the stuff on a sidewall. So, finFET, all of a sudden, put some 3D constructs in there. We had to get better at processes, such as depositing stuff conformally like ALD and etching off sidewalls. You required good process control on sidewalls of structures, rather than just on flat structures. There were process and metrology impacts there. When we go to nanowires, all of a sudden, you are starting to put materials underneath things. So you need more deposition technology for conformality, more etch and etch-control capabilities underneath there, and then also metrology. Measuring what you’ve put in there and measuring the quality of what you’ve built underneath something is challenging.

SE: There are a slew of transistor candidates at 5nm and beyond, such as negative capacitance FETs, tunnel FETs and vertical nanowires. Then, of course, there are post-CMOS devices like spintronics. Any thoughts?

Fried: Tunnel-based devices are pretty interesting. Tunneling is a known phenomenon. The currents that they drive are typically pretty low. But the point is that if we are getting into these regimes where we are going to kill current in favor of electrostatics so that we can scale, all of a sudden maybe these TFETs start to look a little more attractive. There are some pretty interesting devices out there that allow you to scale dimensionally and to scale voltage. So if you get really steep sub-threshold devices you can start going down to quarter-volt technology. It could be a pretty big advantage.

SE: We’ve talked a lot about extreme ultraviolet (EUV) lithography. There are a lot of lesser known challenges like photon shot noise, right?

Fried: EUV is almost there. The question is, ‘Is almost there going to help?’ Our problems are getting to be on the order of the nominal dimensions. Photon shot noise has always been there. We’ve been printing much bigger shapes. So that noise gets hidden in five other variation sources. Now we are down really tight. We’ve gotten rid of a lot of other variation sources. We have a much higher energy and much fewer photons in a much smaller volume. And all of a sudden that variation starts to become the long pole in the tent. It’s not new. We’ll figure it out.

Related Stories

Inside Lithography And Masks

Experts at the table, part 1: EUV’s viability still in doubt even as rollout begins. Uptime and cost are top concerns.

China: Fab Boom or Bust?

A frenzy of activity is causing lots of speculation about how this complex market will evolve.

Next Challenge: Contact Resistance

New materials and tools are needed to solve an issue no one worried about in the past.

Interconnect Challenges Rising

Resistance and capacitance drive need for new materials and approaches.

Uncertainty Grows For 5nm, 3nm

Nanosheets and nanowire FETs under development, but costs are skyrocketing. New packaging options could provide an alternative.

TFETs Cut Sub-Threshold Swing

Devices are still experimental, but they could solve power issues in scaling.

Leave a Reply