Next-gen lithography technology resurfaces for a variety of tasks.

Nanoimprint lithography (NIL) is re-emerging amid an explosion of new applications in the market.

Canon, EV Group, Nanonex, Suss and others continue to develop and ship NIL systems for a range of markets. NIL is different than conventional lithography and resembles a stamping process. Initially, a lithographic system forms a pattern on a template based on a pre-defined design. Then, a separate substrate is coated with a resist. Like a stamping process, the patterned template is pressed against the substrate, forming a pattern on the substrate at feature sizes down to 5nm and beyond.

Fig. 1: Nanoimprint process vs. traditional optical lithography. Source: Canon

Nanoimprint is a cost-effective, single-exposure technique that doesn’t require expensive optics and multiple patterning. But the technology has some issues in terms of defectivity, overlay and throughput, preventing it from becoming a more mainstream lithographic technology. Today, NIL is mainly used for non-semiconductor applications.

It has been promised many times before, but nanoimprint may finally crack the mainstream semiconductor arena. Last year, Toshiba installed Canon’s latest NIL system in a fab in Japan. If all goes well, Toshiba plans to use Canon’s system to pattern some of the features for its devices, as well as next-generation memory types in the future. Production is slated for later this year. “We hope nanoimprint will be ready for production soon,” said Tatsuhiko Higashiki, senior fellow for the Process Technology Research & Development Center at Toshiba Memory. “It is making good progress. However, nanoimprint needs special processes.”

Nanoimprint always had potential, but it must overcome several challenges to get a bigger foothold in the overall lithography market. “We know it is still small compared to mainstream optical lithography,” said Martin Eibelhuber, deputy head of business development at EV Group, a supplier of NIL systems and other products. “However, the use cases for nanoimprinting are increasing rapidly and the CAGR is estimated to be greater than 20%. If new applications for NIL, mainly related to photonics and biotechnology, are accepted by the market, the overall NIL market might even grow to a billion dollars within the next 5 to 10 years.”

NGL shakeout

NIL was originally introduced in 1996, when Princeton Professor Stephen Chou invented the technology and coined the phrase “nanoimprint lithography.” Three years later, Chou founded Nanonex, a pioneer developer of NIL tools. “During the first five years of nanoimprint, most people thought nanoimprint was either impossible or useless, and there were very few people working on it,” Chou said. “The field of nanoimprint has advanced enormously, making significant impact on nanotechnologies and on a broad range of industries.”

In the early 2000s, EV Group, Molecular Imprints (MII), Nanonex, Obducat and other companies began to purse NIL.

Starting in the 2000s, NIL began to move into production, mainly for non-semiconductor applications as well as for some niche-oriented IC products. Over time, the NIL market split into two camps. MII pursued the mainstream lithography market, while others focused on non-semiconductor applications.

Then, with MII in mind, NIL in 2003 landed as a next-generation lithography (NGL) candidate on the old International Roadmap for Semiconductors (ITRS). At the time, 157nm optical lithography, extreme ultraviolet (EUV) lithography, electron projection lithography (EPL) and NIL were listed as NGLs. Later, direct self-assembly (DSA) and multi-beam e-beam landed on the ITRS roadmap.

Originally, MII’s NIL technology was slated for production at the 32nm logic node in 2009. MII’s goal was to compete against EUV lithography or give lithographers another NGL option.

That never happened. The company’s tools were promising in terms of resolution, but they were slow and prone to defects. Funding was (and still is) another issue. Generally, NIL technology had some backing, but it paled in comparison to the billions of dollars spent on EUV lithography.

Over time, several NGL candidates fell by the wayside. 157nm lithography was scrapped. EPL, a technology being developed by IBM and Nikon, was dropped.

DSA, EUV, NIL and multi-beam direct-write survived in the NGL shakeout. But as it turned out, the NGLs took longer to develop and were (and still are) delayed. And thanks to multiple patterning, optical lithography extended further than expected, pushing out the need for the NGLs.

Today, 193nm immersion lithography with multiple patterning remains the workhorse technology at advanced nodes. But it’s becoming more difficult to pattern certain features at 10nm/7nm and beyond.

For logic, the industry is banking on EUV lithography as a means to pattern the most difficult features in chips. EUV is moving closer to production at 7nm and/or 5nm, but there are still several challenges to insert the oft-delayed technology.

The other NGLs, DSA and multi-beam, are targeted for logic. Each lithographic technology will likely find a place at one time or another.

Is NIL ready?

Today, NIL remains viable and is once again divided into two camps—semiconductors and non-semiconductors. Over the years, EV Group, Nanonex and Suss have shown success in the non-semiconductor markets. For example, Nanonex says that it has installed nearly 100 tools in 11 countries since its inception.

And MII continues to pursue the semiconductor market but under a different name. In 2014, Japan’s Canon acquired MII, a move that gave the company some financial backing and technology. MII is now called Canon Nanotechnologies. At present, Canon is focusing its NIL efforts on flash memory with DRAM and other memory types in the future. NIL is ideal for memory, which has built-in redundancy and is more tolerant for defects.

Prior to the acquisition, MII shipped a nanoimprint tool to Toshiba, the biggest proponent of NIL. Originally, Toshiba planned to use MII’s tool for planar NAND flash.

Planar NAND is based on a floating gate transistor structure. Thanks to 193nm wavelength lithography and multiple patterning, vendors have scaled the NAND cell size from 120nm to the 1xnm node regime today, enabling 100 times more capacity.

At 1xnm, though, it is becoming difficult to scale the memory cell and floating gate in planar NAND. So, the technology is running out of steam at the 1xnm nodes.

Planar NAND remains a viable market. But given planar NAND is no longer shrinking, Toshiba decided not to change its lithographic process from immersion/multi-patterning to the NIL tool from Canon in the fab.

Instead, Toshiba now plans to use Canon’s NIL system for the follow-on to planar NAND—3D NAND. “The requirements in lithography for nonvolatile memory devices have been changing from higher resolution technology to a reduction of process cost,” Toshiba’s Higashiki said. “We are planning to apply NIL for 3D NAND at first. Then, we will apply NIL for the next memory such as storage-class memory.”

Toshiba’s 3D NAND partner is Western Digital. In addition, SK Hynix is also developing NIL technology as part of an agreement with Toshiba. So far, though, Intel, Micron and Samsung haven’t announced any plans with NIL.

3D NAND is shipping, but the technology is more difficult to make than previously thought. 3D NAND resembles a vertical skyscraper, in which horizontal levels or layers are stacked and then connected using tiny vertical channels.

Fig. 2: 2D NAND architecture. Source: Western Digital.

Fig. 3: 3D NAND architecture. Source: Western Digital

In the fab, 3D NAND has a different flow. In 2D NAND, the fabrication process is dependent on scaling the dimensions of the memory cell using lithography.

In 3D NAND, the idea is to stack the memory cells on top of each other to scale the bit densities. Lithography is still used for 3D NAND, but it isn’t the most critical step, as the feature sizes are larger. So, in 3D NAND, the challenges shift from lithography to deposition and etch. But 3D NAND still requires some tricky patterning steps, and that’s where NIL fits in—at least for Toshiba.

In the 3D NAND flow, the process starts with a substrate. Then, alternating films are stacked on the substrate using deposition. This process is repeated several times until you obtain the desired layer count on the device. Today, NAND flash suppliers are ramping up 64-layer devices with 96-layer parts in R&D.

Following the alternating stack deposition step, a carbon-based hard mask is applied on the film stack and holes are patterned on the top. For patterning, the industry typically uses traditional 193nm immersion and multiple patterning. In the next step, a plasma etcher then etches tiny circular holes or channels from the top of the device stack to the bottom substrate.

All 3D NAND vendors follow this flow. But going forward, Toshiba hopes to use a different technology for contact hole patterning—NIL. In fact, NIL can be used in other parts of the device. “NIL single patterning without SADP and SAQP is possible to reduce EPE (edge placement error) as well as patterning process cost,” Toshiba’s Higashiki said.

Fig. 4: NIL Process for 3D Memory Source: Toshiba

Fig. 5: 5x-nm Contact Hole Pattern on Wafer with NIL vs. 193nm immersion

But is NIL up for the task? Toshiba and its development partners, such as Canon and Dai Nippon Printing (DNP), appear to have the pieces in place this time around.

In Canon’s NIL flow, the first step is to make a master template, which is based on a quartz or silicon material. The 1X template is made by DNP in a photomask shop.

Using a single-beam e-beam, the tool patterns tiny features on the template based on the desired design. The system enables a template down to 19nm lines and spaces.

DNP continues to use the single-beam tool, but the write times are relatively long. So, DNP has installed a multi-beam e-beam mask writer from IMS Nanofabrication. Using 262,000 tiny beamlets, IMS’ multi-beam mask writer speeds up the patterning or write times on traditional photomasks as well as NIL templates.

“The increased need for precision on the mask, whether for 193i, EUV or NIL, is impacting turnaround times,” said Aki Fujimura, chief executive of D2S, in a recent interview. “The mask industry is looking forward to the improvements in both mask turnaround times and precision that will come from multi-beam mask writing machines.”

Using a multi-beam machine, DNP has devised master templates with line/space features down to 14nm. “The benefit of the multi-beam mask writer is the writing time,” said Koji Ichimura, a technologist from DNP. “We can control the linewidth precisely. We can write any pattern or curvilinear patterns.”

After the master template is made at DNP’s photomask facility, the template is then replicated in a separate system in the same location. Then, the replicated template is shipped to the fab, where it is used in Canon’s NIL tool.

Canon’s latest NIL tool, dubbed the FPA-1200NZ2C, is a 300mm stepper. The four-station cluster system has a 3.4nm overlay and a throughput of 90 wafers an hour, according to Mitsuru Hiura, a technologist at Canon. It is capable of printing sub-10nm feature sizes.

In Canon’s system, a substrate is first moved on a stage. Then, using a “drop-on-demand” inkjet technology, the system dispenses a low viscosity ultraviolet (UV) curable resist on the substrate. The tool dispenses from 10,000 to 100,000 drops with picoliter volumes over a field of 26mm x 33mm, described S.V. Sreenivasan, chief technologist of Canon Nanotechnologies, in the journal Microsystems & Nanoengineering.

The system then takes the template and aligns it to the substrate. The template is then bowed at 10 to 15μm, according to Sreenivasan.

The template makes direct contact with substrate. And with force, the template is pressed against the substrate, forming a pattern with tiny features. Finally, the template is separated from the substrate and the pattern is etched.

Fig. 6: Canon’s Jet and Flash Imprint Lithography (J-FIL) technology Source: Canon, Microsystems & Nanoengineering/Nature

NIL faces the same challenges. First, the template must be defect-free. Otherwise, it will cause repeating defects on the substrate. Defectivity and overlay remain issues, but the tool is making progress. “We are optimizing device processes for production and improving the NIL tool, such as overlay accuracy, throughput and defect reduction. We hope to start producing devices with NIL later this year,” Toshiba’s Higashiki said.

Canon’s NIL technology stands a chance this time around. “Optical lithography just keeps extending, but Canon will have a chance. But it just takes a long time to replace an existing technology,” Nanonex’ Chou said.

Other applications

Generally, though, NIL has been more successful in markets beyond semiconductors. “(This includes) nanophotonics, smartphones, displays, light emitting diodes, solar cells, optical communication, semiconductor ICs, data storage, biotechnology, pharmaceutics, medicine and security features,” Chou said.

NIL succeeds in markets where it doesn’t necessarily compete against existing lithographic techniques. “NIL has long been considered a technology that is in competition with mainstream lithography technologies that have been established for many years,” EV Group’s Eibelhuber said. “We see NIL as an extension in the lithography toolbox for different patterning requirements. In other words, NIL addresses new markets rather than challenging optical lithography or EUV in the IC logic and memory markets.”

In this segment, NIL suppliers sell tools based on various techniques, such as hot embossing, UV-based NIL and soft lithography.

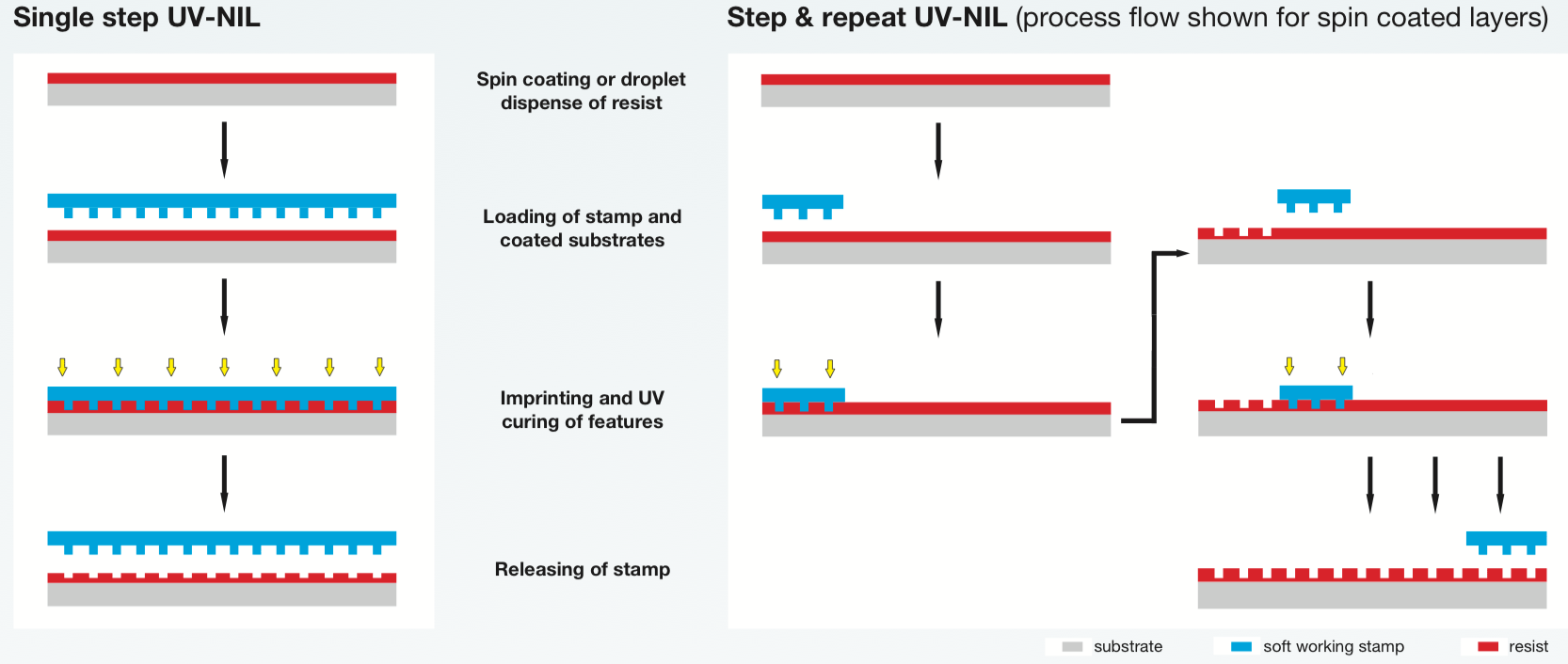

Each vendor has different tools and flows. For example, EV Group has a single-step NIL flow. It also has a separate step-and-repeat process. Both enable resolutions below 15nm.

Fig. 7: EV Group’s NIL process flows Source: EV Group

“Today, we see two key areas where the benefits of wafer-level NIL processes are being explored. These are photonic and biotechnology applications, as their pattering requirements fit perfectly with the strength of nanoimprint lithography,” Eibelhuber said.

There are other possibilities. For example, Leti recently launched an NIL program, dubbed INSPIRE. The program is using EV Group’s NIL tools. “We are not addressing the CMOS market,” said Laurent Pain, patterning program manager at Leti. “We are investigating it for LEDs. There are also a lot of applications for biotechnology, microfluidics or DNA sequencing.”

What’s next? EV Group and SwissLitho recently announced a partnership to enable the production of 3D structures down to 1nm.

SwissLitho develops a thermal scanning probe lithography system. Invented by IBM, thermal scanning probe lithography is a maskless, direct-write lithography technique.

In the flow, a resist is spin-coated on a substrate. Then, a heated ultra-sharp tip is used to decompose and evaporate the resist, creating tiny nanostructure patterns.

As part of the deal with EV Group, SwissLitho’s technology will be used to produce master templates with 3D structures for NIL. EV Group’s NIL tools will replicate those structures. The applications include the development of diffractive optical elements and photonics.

To be sure, NIL enables a wide range of apps. It’s still unclear if it’s ready for 3D NAND. If it does work, Toshiba might get a leg up on its rivals. It’s a risk worth taking.

Related Stories

Ready For Nanoimprint?

Behind The Scenes In Nanoimprint Lithography

EUV’s New Problem Areas

DSA Re-Enters Litho Picture

Thank you for sharing this inspiring article. NIL will be a great addition and a good compliment to manufacturing strategy.

You state: “The template makes direct contact with substrate. ”

The mask does not directly contact the substrate. This would be detrimental to mask defectivity. The mask actually makes contact with the dispensed fluid which acts as a buffer to prevent process induced mask defects.

Hi Chris, Thanks for the clarification.

Has NIL been investigated to make perfect filters with perfect hole sizes, thinner fine membrane layers, higher flows vs pressure?