Contacts and interconnects becoming more problematic at each new node, but with fixes come tradeoffs.

Chipmakers continue to scale the transistor at advanced nodes, but they are struggling to maintain the same pace with the other two critical parts of the device—the contacts and interconnects.

That’s beginning to change, however. In fact, at 10nm/7nm, chipmakers are introducing new topologies and materials such as cobalt, which promises to boost the performance and reduce unwanted resistance in chips. It’s still too early to say if the changes will work. Early reviews are mixed.

To be sure, though, there is an inflection point taking place in leading-edge chips, which consist of three parts—the transistor, contacts and interconnects. The transistor resides on the bottom of the structure and serves as a switch. The interconnects, which reside on the top of the transistor, consist of tiny copper wiring schemes that transfer electrical signals from one transistor to another.

The transistor structure and interconnects are connected by a layer called the middle-of-line (MOL). The MOL layer consists of a series of tiny contact structures.

Fig. 1: Interconnect, contact and transistor at various nodes. Source: Applied Materials.

The biggest challenges in chip scaling involve the contacts and interconnects. In fact, the interconnects are becoming more compact at each node, causing an unwanted resistance-capacitance (RC) delay in chips. “There is the transistor, which is the finFET. That’s getting better and better as things get smaller,” said Jonathan Bakke, global product manager at Applied Materials. “The counterparts are the contacts and interconnects. As those get smaller, they actually get worse because the resistance goes up. That’s what we need to de-bottleneck.”

There are myriad issues in this segment. “It starts with contact resistance to the silicon. Then, it gets into items like electromigration and so forth with copper,” said Klaus Schuegraf, vice president of new products and solutions at PDF Solutions. “It’s also quite complicated to do the integration with a new material. That’s why everybody is looking at it a little bit differently.”

To solve the problems, chipmakers are implementing new schemes at 10nm/7nm. Then, fab tool vendors have new solutions. Here are the major events in this area:

• Traditionally, chipmakers use tungsten for the contacts. At 10nm, Intel switched from tungsten to cobalt. Others are following suit at 7nm or considering the idea.

• For years, chipmakers have used copper as the interconnect metal in chips. Intel moved to cobalt for some layers, but not all, at 10nm. Others appear to be sticking with copper at 7nm, as cobalt has some tradeoffs.

• Ruthenium and other materials are being explored in R&D.

• On the equipment front, Applied Materials, Lam Research and others are developing new systems to enable cobalt structures in devices.

MOL challenges

Typically, transistors are manufactured in the front-end-of-the-line (FEOL) in the fab. The interconnects and contacts are made in a different part of the fab called the backend-of-the-line (BEOL). In the BEOL, chipmakers deal with the metallization processes, which are fabricated separately from silicon-based transistors. Metals can poison silicon if they mix.

In a process flow, a chipmaker first develops the transistor. Then, contacts are formed on top of the transistor using a different process.

Contacts are three-dimensional structures with a small gap, which is filled with tungsten, a conductive material. The tungsten structure, called a tungsten plug, is sandwiched between a liner material (titanium) and a barrier layer (titanium nitride). The entire structure is called a contact.

Starting at 22nm/20nm, chipmakers introduced a new layer called the MOL. The contacts (tungsten plugs) are situated in the MOL layer.

Contacts presented few challenges for planar devices, but it’s a different story in the MOL layers at advanced nodes. “It is very, very complex,” said David Fried, vice president of computational products at Coventor, a Lam Research Company. “You have all the topography of the front-end. You’re using materials that are typically less rigid, less stable and less comfortable than you would like to use on the front end. And then the design constructs present in middle-of-line are much more complex than anything you’d see on the back-end.”

Still, chipmakers have extended tungsten-based contacts to 16nm/14nm. But here, the volume of the tungsten conductor material is relatively small. So a signal must flow through a smaller amount of conductive metal, causing a big problem in chips—contact resistance. Resistance relates to the difficulty to pass a current through a line or conductor.

Contact resistance becomes more problematic at each node. At 16nm/14nm, the critical dimensions (CDs) for the contact is 25nm. “At the 10nm node, you would have roughly a 20nm CD,” Applied’s Bakke said. “At 7nm, it’s 15nm plus or minus a few nanometers. By the time you get to 15nm, you only have 3nm of tungsten (in the contact). That means your resistance is skyrocketing.”

In addition, tungsten is running out of steam for contacts. “Tungsten has by far the best reliability of all of these metals. But the fact is that it breaks in terms of gap fill and resistance,” Bakke said. “You actually hit the limit at 12nm. You physically can’t scale tungsten anymore.”

So chipmakers are making some changes. Intel, for one, switched from tungsten to cobalt for the MOL contacts at 10nm, saying it provides a 60% reduction in line resistance. Some chipmakers are following suit at 7nm. Others may take a wait-and-see approach.

Fig. 2: FinFET at 16/14nm, 10nm, 7nm. Source: Applied Materials

Cobalt has some advantages. “Compared to tungsten, cobalt offers inherently superior resistance at small dimensions, given its ability to fill small features with a much thinner barrier,” Bakke said in a blog.

It remains to be seen if cobalt contacts can live up to their promise. The chips are just beginning to ramp up, but it will take time before the results are tabulated.

The key metrics are yield and reliability. “Obviously, there is a challenge with contact resistance. But then the question is what the defectivity of the contacts and the variability of the contacts. That’s a big challenge,” PDF Solutions’ Schuegraf said.

On the equipment front, meanwhile, chipmakers use deposition tools to deposit tungsten materials for contacts. Recently, Applied Materials introduced a suite of tools that enables a cobalt fill process for the contacts as well as the interconnects. Others are working on similar products.

BEOL blues

While chipmakers are addressing the MOL, they also have their sights set on the other problematic part of the chip–the interconnects.

Interconnects are the tiny copper wiring schemes in chips. “These wires function like highways or pipelines to transport electrons, connect transistors and other components to each other, and make them functional,” explained Larry Zhao, a technical director at Lam Research, in a recent blog.

Today’s leading-edge logic chips have 9 to 12 metal layers or more. Each layer, which has a wiring scheme, is connected to another layer with vias. In total, a leading-edge device may incorporate around 30 miles of interconnect wires.

Fig. 3: Interconnect Layers Source: Lam Research

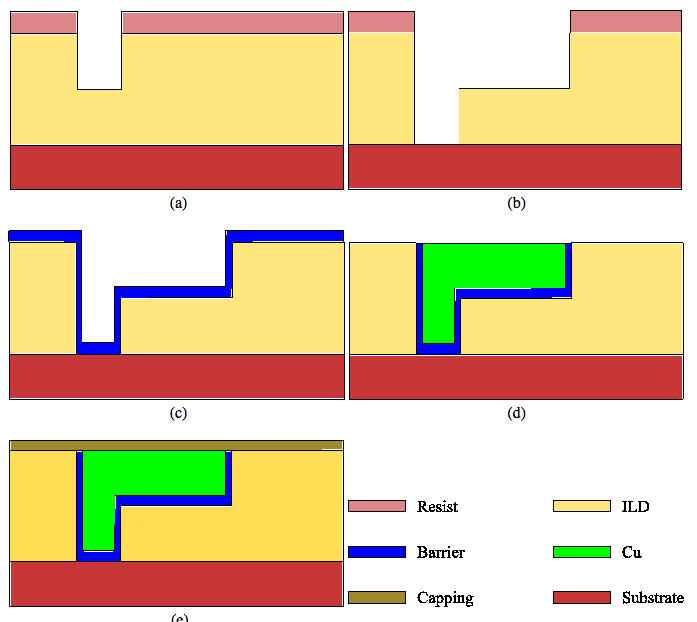

For years, the industry has used a dual damascene process to make the copper interconnects in chips. In this flow, a low-k dielectric material is first deposited on the surface of the device. Based on a carbon-doped oxide material, low-k films are used to insulate one part of the device from another. The films also reduce parasitic capacitance in the interconnects.

Fig. 4: Dual-Damascene Fabrication Process. Source: R. L. de Orio: Electromigration Modeling and Simulation

Low-k films are characterized by a dielectric constant, or “k value.” Today’s low-k films have a “k value” of about 2.5 or 2.6. At one time the goal was to reduce the “k value” to about 2.2, which would further reduce the parasitic capacitance. But at 2.2 and below, chipmakers found that these low-k materials are prone to damage during the process and packaging flows. So the industry is stuck at the same “k” values.

To help solve the problem, Intel incorporated air gaps on one layer of the interconnect stack at 14nm. Air gaps lower the capacitance, but they also add cost to the process, so they will be implemented in some but not all chip designs.

Meanwhile, after the low-k film is deposited, the next step is to pattern the vias and trenches on the film. The structure is etched, forming a via and trench.

Then, inside the trench, a thin barrier layer (tantalum nitride) and liner layer (tantalum) are deposited. But at advanced nodes, the liner/barrier film is taking up too much room. So starting at 20nm, some chipmakers replaced tantalum with cobalt for the liner. Cobalt reduces the thickness of the liner. The barrier layer is still tantalum nitride.

Finally, the via/trench structure is filled with copper using electrochemical deposition (ECD). The process is repeated multiple times at each layer, thereby creating a copper wiring scheme.

The dual damascene process, however, began to show cracks at 22nm/20nm, when the copper interconnects became more compact, causing RC delays in chips. “R” is the resistance of a material, while “C” is the capacitance.

“As transistors have gotten smaller and smaller, interconnects also have had to scale in size. Today, we’re at the point where conventional copper interconnects are facing a significant roadblock to further scaling, and that roadblock is known as the RC challenge,” Lam’s Zhao said. “Looking at the ‘R’ side of this challenge, higher-resistance lines carry less current, which slows device speed.”

Fig. 5: Higher resistance with a smaller line width. Source: Lam Research

For years, the industry has been looking at ways to solve the problem. For example, ruthenium has been proposed to replace cobalt for the liner. Ruthenium has good gap fill properties, but it’s difficult to polish.

A more radical step is to replace copper in the interconnects. Cobalt and ruthenium have been proposed, but until recently that was considered too expensive and difficult.

At 10nm, Intel took a bold step as it moved from copper to cobalt interconnects for some but not all layers. Not all chipmakers are following suit, however. “It is important to note that for wide features, copper is still the metal of choice. Cobalt is not going to completely replace copper. It’s just going to be another tool in the tool set when you are looking at interconnects,” Applied’s Bakke said.

Copper has a lower resistance than cobalt, but copper suffers from other issues. Copper has an electron mean free path of 39nm. “The electron mean free path defines the length that an electron travels in a bulk material without scattering,” Bakke said in a blog. “When features are below the mean free path, significant scattering occurs at material interfaces and grain boundaries, causing increased resistance.”

In comparison, cobalt has a mean free path of about 10nm. The crossover point when cobalt interconnects have a lower resistance than copper is in the 10nm to 15nm range, according to Applied.

Intel’s 10nm process, meanwhile, features 13 metal layers. The first two layers, called metal 0 (M0) and metal 1 (M1), are fabricated using self-aligned quadruple patterning. M1 has a 36nm pitch, which is a 0.51X scaling boost over its 14nm process.

What’s different is that Intel’s local interconnect layers—M0 and M1—incorporate cobalt, not copper, as in previous technologies. The remaining layers use traditional copper metal.

Intel’s M0 and M1 layers consist of short cobalt wires. Each cobalt wire is separated with a dielectric material based on aluminum oxide.

Cobalt-based interconnects have some tradeoffs. “In this particular case, we chose cobalt for practical reasons. It has excellent gap-fill using a Ti-based liner,” said Andrew Yeoh, process integration manager at Intel, in a presentation at the recent IEEE International Interconnect Technology Conference (IITC).

“Cobalt’s properties provide the required excellent electromigration resistance for high-performance designs,” Yeoh said in a paper at IITC. “At the short range routing distances typical of M0 and M1, the intrinsic resistance penalty of cobalt (versus copper) is negligible, especially when the true copper volume at sub-40nm pitches is considered.”

There are some drawbacks, however. Overall, cobalt suffers approximately a 1.7X line resistance penalty compared to copper, for the metal pitch in question, he said. “It is not as good as copper. We haven’t hit the crossover.”

So most other chipmakers are sticking with copper for the interconnects at 7nm. By tweaking copper, vendors have eked out enough gains to extend the incumbent technology. For example, GlobalFoundries’ 7nm finFET process has a metal pitch of 40nm. Unlike Intel, GlobalFoundries is using self-aligned double patterning with copper interconnects. “We made improvements in the copper wiring at about 100X for electromigration. So we are able to stay in copper, which has some advantages in yield and complexity,” said Gary Patton, CTO of GlobalFoundries.

Others see similar results. “We’ve evaluated cobalt interconnects. At these dimensions, we still see almost a 2X line resistance increase over copper. Even for the next generation, we see that it doesn’t quite cross over,” said Daniel Edelstein, a fellow and manager of processes, materials and integration at IBM.

Indeed, the industry believes it has found ways to extend copper for the interconnects at 5nm. Still, others may switch to cobalt for some layers. Even ruthenium is being considered.

Regardless, the industry will not only require new materials, but new processes. For example, GlobalFoundries and Imec have presented papers about new fully self-aligned via processes at 5nm and beyond.

Fully self-aligned vias is a method of connecting two metal lines on different levels. Self-aligned vias as well as self-aligned contacts are called scaling boosters, which will enable IC scaling in chips.

Scaling boosters will require new tools and materials. “We need to introduce some performance boosters,” said Kandabara Tapily, a researcher at TEL, in a presentation at IITC. “For this, we believe selective deposition and selective etch will be fundamental for those nodes coming in.”

Selective processes will be required for transistor scaling. “That’s also true for middle-of-line all the way to the backend-of-the-line in order to address some of the EPE issues that we face,” Tapily said.

The solutions

The industry will require other new tools for MOL/BEOL. As stated, Applied has developed products for the cobalt fill process.

Meanwhile, at IITC, Lam Research presented a paper about a different cobalt fill technology. Lam’s cobalt via-prefill process uses ECD. It fills the via from the bottom up.

In addition, chipmakers will require new inspection/metrology technologies. “Scaling boosters are appearing in the BEOL. These include self-aligned vias and super vias. These are challenging processes with narrow process windows and have resulted in new applications for optical-based CD (OCD) metrology and optical inspection,” said John McCormack, technical director of process control solutions at KLA-Tencor.

“On-product overlay, CD uniformity and hot spots (design or process systematic defects) are becoming more interconnected. The interaction of multiple process steps determines the final pattern, making it more difficult to identify the source of patterning variation,” McCormack said. “This drives the need not only for monitoring fab-wide process steps, but also for implementing multiple inspection and metrology measurements at the same process step – to find, fix and prevent errors from moving downstream.”

Related stories

The Week In Review: Manufacturing (Applied’s cobalt rush; China DRAM probe; trade issues.)

New BEOL/MOL Breakthroughs?

The Race To 10/7nm

BEOL Issues At 10nm And 7nm

Next Challenge: Contact Resistance

Great story, Mark.

I arrived at the conclusion that Intel’s switch to cobalt is premature (among other things) independently, without contacting people involved, and before Intel’s IITC paper and recent publications from Applied Materials became available, which, along with your article is a great proof of my previously published analysis. My main clues was research on copper deposition techniques and respective resistivity figures.

Please keep covering this topic — by asking pointed questions you can elicit more shocking truth about Intel’s 10nm process tech than what already meets the eye from their IITC paper, e.g. resorting to quintuple and sextuple patterning, never-announced use of ruthenium, which Techinsights found in the i3-8121U, reliability problems, more severe hotspotting, and probably more.

To everyone reading this comment: please don’t take my writeup as some kind of ultimate indisputable truth from an expert. I started sharing my thoughts on Intel’s 10nm tech out of frustration at total lack of analytics on this interesting topic, so enjoy my posts and let me know what you think on this subject.

I post this comment here in hope to

– read more at semiengineering.com on the interesting subject of Intel’s problems with their 10nm tech and

– spark some interest and hear back from people — in the first place from 3 groups: those who, like me, put some thought into this matter and have something interesting to say, or can speak from experience on the topic, or have inside knowledge to share. But of course other comments are welcome as well.

Resistance is the one thing that has always scaled adversely, and that limits “clock reach” – meaning you have to buffer stuff more anytime you shrink in order to keep speed up (clock rates), which is why CPUs have been flat-lined at 3GHz for years. Likewise dropping V to keep power down impacts margins and the ability to drive current through the higher resistance.

As with hoping EUV would get to the next nodes, I don’t think there’s a fix for this (bar finding a room-temperature superconductor).

There are alternatives to RTL, which could go faster, just not much of a tool flow to support them.