New approaches aim to drive down cost, boost benefits of heterogeneous integration.

Several companies are racing each other to develop a new class of 2.5D and 3D packages based on various next-generation interconnect technologies.

Intel, TSMC and others are exploring or developing future packages based on one emerging interconnect scheme, called copper-to-copper hybrid bonding. This technology provides a way to stack advanced dies using copper connections at the chip level, enabling new types of 3D-ICs, chiplets and memory cubes. Still in R&D, copper hybrid bonding and competitive schemes are promising, but they also present some technical and cost challenges.

Many companies and research organizations are working on it, and for good reason. In some cases, traditional system-on-a-chip (SoC) designs are becoming too unwieldy and expensive at advanced nodes. So the industry is scrambling to develop new device alternatives using a multitude of different approaches.

Today, meanwhile, the industry is developing or shipping 2.5D/3D and other advanced packages using existing interconnect schemes. Interconnects are used to connect a die to another die or to a separate interposer as in 2.5D. In many of these packages, the dies are stacked and connected using an interconnect technology called copper microbumps and pillars. Bumps and pillars provide small, fast electrical connections between different devices.

The most advanced microbumps and pillars are tiny structures with a 40μm pitch. A pitch refers to a given space. A 40μm pitch involves a 25μm copper pillar in size with 15μm spacing. Going forward, the industry can scale the bump pitch possibly at or near 20μm. Then, the industry needs a new interconnect solution beyond bumps and pillars.

There are several options on the table, but copper-to-copper hybrid bonding is the current favorite. The idea to stack and connect dies directly using a copper-to-copper diffusion bonding technique, eliminating the need for bumps and pillars.

“A number of organizations and companies are planning to adopt direct bond interconnect or hybrid bonding as they get to 20μm to 10μm and below pitches,” said Jan Vardaman, president of TechSearch International. “It will probably be necessary as we go to a 10μm pitch and below.”

Copper hybrid bonding isn’t new. For years, the technology has been used for advanced CMOS image sensors. But migrating the technology for advanced chip stacking, such as memory on memory and memory on logic, is challenging and involves complex fab-level processes. And the timing of the technology remains a moving target, although the first products may appear by 2021 or sooner.

Nonetheless, there are several developments in the arena. Among them:

Also in R&D, many are working on new 2.5D, 3D-IC and chiplet designs, which stack memory on logic or logic on logic.

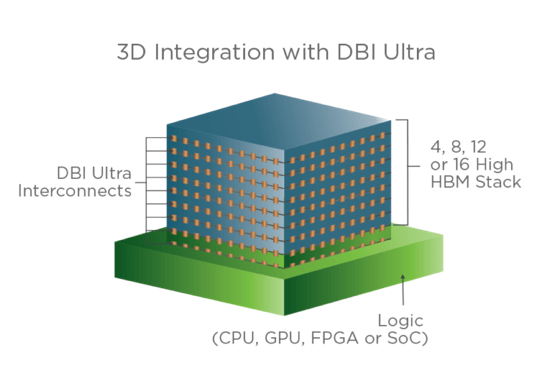

Figure 1: 3D integration with hybrid bonding Source: Xperi

Interconnect challenges

Today’s chips are housed in a plethora of IC package types. One way to segment the packaging market is by interconnect type, which includes wirebond, flip-chip, wafer-level packaging (WLP) and through-silicon vias (TSVs). These aren’t package types per se, but they designate how chips are connected to each other or onto the board.

Some 75% to 80% of today’s packages are based on wire bonding, according to TechSearch. A wire bonder stitches one chip to another chip or substrate using tiny wires. Wire bonding is used for many package types.

For many chips, wirebond doesn’t provide enough I/Os. To increase the I/Os, the industry uses different interconnect technologies, such as flip-chip, WLP and TSVs.

“All these technologies have their own unique sweet spot for different applications,” said Calvin Cheung, vice president of engineering at ASE. “If you look at the roadmaps, you can divide it into flip-chip, fan-out and 2.5D in density and package size. Density refers to the number of I/Os. Right now, 2.5D can handle the most I/Os. 2.5D can handle I/Os and power grounds in excess of more than a few hundred thousand bumps. For fan-out, it’s a medium-size density and package size. Then, for BGA, you are talking about a few hundred to a thousand I/Os.”

In flip-chip, a sea of larger solder bumps, or tiny copper bumps and pillars, are formed on top of a chip. The device is flipped and mounted on a separate die or board. The bumps land on copper pads, forming an electrical connection. Generally, the two structures are bonded using a system called a wafer bonder. The less aggressive pitches use a flip-chip bonder.

Fan-out is classified as WLP, where dies are packaged while on a wafer. Meanwhile, in 2.5D, dies are stacked or placed side-by-side on top of an interposer, which incorporates TSVs. The interposer acts as the bridge between the chips and a board.

Advanced packaging, such as 2.5D and fan-out, has been around for years. But it is mainly used for higher-end applications. It’s too expensive for many products.

Going forward, though, advanced packaging is expected to become a more viable option to develop new system-level chip designs. The traditional approach of scaling chips, to pack in more transistors, is becoming more difficult and expensive at each new node. So while scaling remains an option for new designs, the industry is searching for alternatives.

Another way to get the benefits of scaling is by putting multiple and complex chips in an advanced package, also known as heterogeneous integration. In one example of heterogeneous integration, chipmakers can incorporate an FPGA and an HBM in a 2.5D package. Targeted for high-end systems, HBM stacks DRAM dies on top of each other and connects them with TSVs, enabling more I/Os and bandwidth. For example, Samsung’s HBM2 technology consists of eight 8Gbit DRAM dies, which are stacked and connected using 5,000 TSVs.

In HBM, each DRAM die has microbumps on both sides, enabling a connection to another die. “We are talking about a 5µm TSV through 50µm thick DRAM dies, and microbumps with a 25µm diameter with a 55µm pitch,” said Thomas Uhrmann, director of business development of EV Group.

Getting back to the 2.5D example, the HBM and the FPGA are then stacked, connected and bonded to the interposer using tiny copper microbumps with 55µm pitches.

The bonding process isn’t done with a flip-chip bonder. For finer pitch requirements, the industry generally uses thermal compression bonding (TCB). A TCB bonder picks up a die and aligns the bumps to those from another die. It bonds the bumps using force and heat.

“TCB defines the formation of fine-pitch interconnects using force during soldering rather than reflow soldering. The lower the interconnect pitch gets, the higher the requirements are for flatness and deformation during bonding,” Uhrmann said.

Nonetheless, there are several nagging issues with today’s 2.5D and 3D technologies. Cost is one issue. In addition, TCB is a slow process with low throughputs.

“Many customers are going in the third dimension by stacking chips. Every time they are stacking chips, they have thousands of bumps or pillars. They have to glue those things to each other as they keep stacking up layers. All of the bumps or pillars need to be at the same height. Otherwise, the bumps don’t make contacts. Then, you basically could lose your entire package,” said Subodh Kulkarni, president and chief executive at CyberOptics.

Going forward, leading-edge chip customers are migrating to the next nodes at 10nm/7nm and beyond. This has several implications for the package. “You need more I/Os. You are able to integrate more functional blocks into the die. So you need more I/Os to route the functions,” ASE’s Cheung said.

To put more I/Os in the same area, you need to shrink the bump pitch beyond today’s 40µm spec. That requires smaller bumps and pillars. Using today’s technologies, the industry sees a path to scale the bump pitches around 20µm. This still remains a moving target, however.

Today, there are some examples in the market. Intel, for one, recently unveiled a new 3D CPU platform, code-named “Lakefield.” This combines a 10nm processor core with four of Intel’s 22nm processor cores into a package. The 3D technology, called Foveros, uses existing microbumps with a 36µm pitch, according to WikiChip, a Web site.

Over time, many will stay at the current bump pitches. Some will push them to the limits. Beyond a certain point, though, there are some challenges with bumps and pillars.

In the copper pillar process flow, the dimensions of the pillars are defined. Then, on a substrate, the surface is deposited with a seed layer. A resist is applied on the surface and then patterned. A copper layer is plated in the defined area, followed by a solder cap.

At 20µm pitches, the process becomes difficult. A 20µm pitch involves a 11 to 12µm pillar size with 8 to 9µm spacing. That’s when the aspect ratios of the pillars become difficult to manage and control.

“The minimum microbump pitch can go below 20µm from a lithography standpoint. The minimum microbump CD is determined by the photoresist chemistry, the microbump height, and the numerical aperture of the imaging lens. The CD challenge for microbumps comes from other process steps such as the undercut of the copper seed layer during wet etch,” said Shankar Muthukrishnan, senior director of lithography marketing at Veeco.

What is hybrid bonding?

Nonetheless, the industry requires a new interconnect solution around a 20µm pitch. The leading contender is copper-to-copper bonding. The idea is to stack and connect devices directly using fine-pitch copper connections, not microbumps and pillars.

There are several approaches here, such as copper-to-copper thermal compression bonding and copper-to-copper hybrid bonding.

Kulicke & Soffa and UCLA recently demonstrated a copper-to-copper TCB technology, enabling fine-pitch copper interconnects at ≤10μm. Researchers also develop an in-situ treatment, which reduces copper oxidation.

In copper TCB, the idea is to form copper pillars on the surface of two wafers. The pads are then bonded using TCB. Still in R&D, copper TCB faces some reliability and cost challenges.

Copper-to-copper hybrid bonding, meanwhile, has the most momentum. With the technology, Intel, TSMC and others are exploring or devising a new class of fine-pitch 2.5D and 3D-ICs. TSMC recently provided more details about its next-generation 3D technologies, called System on Integrated Chips (SoIC) for 3D heterogeneous integration. Still in R&D, SoIC will use fine bump pitches with copper hybrid bonding.

TSMC and others are developing their own hybrid bonding technology. One company, Xperi, develops and licenses its own technology to others.

In hybrid bonding, you bond two structures together using different materials with a wafer bonder. Some are using standard materials, while others are exploring more exotic types like nano-pastes and nano-particles.

“Hybrid bonding is all about making good electrically conductivity between two die, and there are many methods to consider,” said Johanna Swan, director of packaging research and fellow at Intel. “We are looking at a slew of different materials based on what we think is best for our products.”

Hybrid bonding is different from a technology called “direct bonding,” which is used for today’s CMOS image sensors, MEMS and RF switches.

In direct bonding, a wafer is processed in a fab. Dielectric materials are exposed on one side of the wafer. Another wafer is processed the same way. Then, the two wafers undergo a dielectric-to-dielectric bonding process using a wafer bonder.

In hybrid bonding, the process is somewhat similar. The difference is that the two wafers are bonded together using a combination of two technologies—a dielectric-to-dielectric and a metal-to-metal bond—all at room temperature. In this case, the metals involve a copper-to-copper bond.

Hybrid bonding can be used to bond two wafers together (wafer-to-wafer bonding) and a chip to a wafer (die-to-wafer bonding).

The hybrid bonding process is conducted in a front-end manufacturing flow in a fab, not at an OSAT. “We’re riding the coattails of front-end processes,” said Craig Mitchell, president of Invensas, which is part of Xperi. “We have to optimize the parameters for our application, but we are using existing equipment.”

Xperi refers to its hybrid bonding process as Direct Bond Interconnect (DBI). DBI follows a traditional copper damascene flow in a fab.

Once a wafer is processed in the fab, metal pads are recessed on the surface. The surface is planarized using chemical mechanical polishing (CMP). Then, the wafer undergoes a plasma activation step.

A separate wafer undergoes a similar process. The wafers are bonded using a two-step process. It’s a dielectric-to-dielectric bond, followed by a metal-to-metal connection.

Hybrid bonding works. For years, the industry has been using the technology to make advanced CMOS image sensors. For this, one wafer is logic while the other is a pixel array. The two wafers are bonded together.

Years ago, Sony licensed Xperi’s hybrid bonding technology for use in developing image sensors. Used in today’s smartphones, Sony’s image sensor consists of 6μm pitch interconnects.

“We’ve also demonstrated 1.6μm,” said Abul Nuruzzaman, senior director of product marketing at Xperi. “The industry has been talking about 1μm pitches.”

All told, hybrid bonding enables 250,000 to 1 million interconnects per square millimeter. In comparison, 40μm pitch microbumps enables 600-625 interconnects per square millimeter.

Now, the industry is working on hybrid bonding for advanced memory and logic die stacking. The goal is to develop more advanced 2.5D/3D products.

This is where the industry faces several challenging, which is why it’s still in R&D. “Achieving a good copper-to-copper bond requires precise control over the topography following the copper CMP step,” said Stephen Hiebert, senior director of marketing at KLA. “If overpolished, the copper pad recess gets too large and there is a risk the pads will not join during hybrid bonding. If underpolished, copper residues can create electrical shorts.”

Meanwhile, Xperi has developed a new version of its hybrid bonding technology. This version is geared for die-to-wafer stacking with 40μm to 1.6μm pitches.

For this, the hybrid bonding process flow is the same, but there are more steps. Once the wafer is processed, the chips are diced, activated and then bonded on a wafer. “We see this as a critical solution for 2.5D and 3D integration moving forward,” Invensas’ Mitchell said. “For many 2.5D and 3D applications, you’re going to source dies that are of different sizes. They may come from different wafers, and even different fabs. Having a technique that allows you to take an individual die that’s known good and bonding it to another die that’s known good is an important capability for future electronics.”

Initially, Xperi’s new hybrid bonding technology is targeted for a new class of 3D memory, which will ship in the next two to three years. For example, the industry is developing 3DS DRAMs. Then, for HBM, 16 DRAM dies could be connected directly to each other with fine-pitch copper connections. It still requires TSVs between each layer.

Another application involves 2.5D, 3D-ICs and chiplets, where you stack memory-on-logic or logic-on-logic at the chip level. “Where we see this headed is in 2.5D and true 3D-IC chiplet concepts, allowing for a whole set of much higher density interconnects between those chiplets. You are getting to a point where you have almost chip-like interconnects, but you are able to use that between chips,” Mitchell said.

There are other advantages. “As chips get larger, the distances to travel from one end of the chip can get significant. But if you have three-dimensional interconnects, you get to microns,” he said. “This is important for power, latency, performance and heat. If you don’t have to drive a signal over a large area, you can use less current. This generates less heat.”

The new hybrid bonding technologies from Xperi and others aren’t simple and present some major challenges. “As people get to these kinds of pitches, you are going to need a front-end mentality,” TechSearch’s Vardaman said. “The environment has to be super clean. There can be no particles on the surface. Otherwise, you don’t have a bond. There’s a lot of issues to deal with.”

Those aren’t the only challenges. “Even more challenging are multiple layers or chip stacks, as sequential non-uniformities during bonding are influencing the next layer bonding. Therefore, tolerances and uniformity requirements are increasing. Even more importantly, the value of the die stack is rapidly increasing, meaning the cost of yield is increasing,” EV Group’s Uhrmann said.

Others agree. “For multiple devices combined in heterogeneous integration, one bad die results in the failure of the whole package,” KLA’s Hiebert said. “For hybrid bonding, we see several process control challenges that must be overcome to drive adoption of the technology into new logic and memory applications. Voids severely limit yield in hybrid bonding, so inline defect inspection for void-inducing particles is essential. For pitches less than 10µm, detection of particles in the 100nm to 200nm range becomes critical.”

Some issues aren’t so obvious. “Temporary bond/debond processes are needed for advanced 2.5D and 3D packages, but it really depends on what the end goal is,” said Kim Arnold, executive director for the advanced packaging business unit at Brewer Science. “The challenge for some processes is that they utilize a flip process, which requires two carriers. This means that ‘carrier 2’ has to withstand the debond method for ‘carrier 1.’ ”

Conclusion

Clearly, hybrid bonding is complicated. But the industry wants to make it work. As chip scaling slows down and is becoming too expensive, the industry needs some new and different approaches.

Otherwise, the IC industry itself may slow, if not grind to a gradual halt. It might be there already.

Related Stories

DBI© was developed & trademarked by Ziptronix, then transferred to Invensas via Xperi. Is the hybrid bonding described here different from the DBI© as practiced under license?

Ziptronix presented DBI technology at multiple 3DI sessions since 2005 – 6. I have had the pleasure of working with their team from 2007 till 2011.

Hi Gretchen,

Generally, in the article, I was describing Xperi’s DBI hybrid bonding process to enable 3D integration. Others are also working on hybrid bonding processes for 3D integration. Each one may be the same or slightly different.

In the article, I was also trying to describe the challenges with hybrid bonding processes in general.

FYI. Xperi’s DBI technology was originally developed by Ziptronix. In fact, Ziptronix developed two wafer bonding processes—ZiBond and DBI. ZiBond is direct bonding, while DBI is hybrid bonding.

In 2015, Tessera acquired Ziptronix for $39 million. Tessera is part of Xperi.

To back claims that DBI is ready to replace current die stacking / bonding technologies ( TC FCB w/ Sn capped Cu uPillar bumps ) in products like HBM, it is necessary to present data beyond just PowerPoint sketches of stacks. This has not been seen in publications and presentations till Jul 2020. What is necessary are (1) description of the Stacked Test Vehicles incl. x sections showing the interconnect stack (2) details to assess if they replicate the essential features of vertical interconnects in HBM ( i,e. the over 5,000 TSVs in the central area of the stack if necessary modified for DBI ) (3) description of the Daisy Chains tested (4) yield and reliability test results for multi die stacks